#### ABSTRACT

# ZHU, YIFAN Dynamic Voltage Scaling with Feedback Scheduling for Real-time Embedded Systems.(Under the direction of Dr. Frank Mueller).

Dynamic voltage scaling (DVS) is a promising method to reduce the power consumption of CMOS-based embedded processors. However, pure DVS techniques do not perform well for dynamic systems where the execution times of different jobs vary significantly. A novel DVS scheme with feedback control mechanisms for hard realtime systems is proposed in this work. It produces energy-efficient schedules for both static and dynamic workloads. Task-splitting, slack-passing and preemption-handling schemes are proposed to aggressively reduce the speed of each task. Different feedback control structures are integrated into the DVS algorithm to make it adaptable to workload variations. This scheme relies strictly on operating system support. It is evaluated in simulation as well as on an embedded platform. For given task sets, simulation experiments demonstrate the benefits of this scheme with savings of up to 29% in energy over previous work. This scheme exhibits up to 24% additional energy savings over other DVS algorithms on the embedded platform. The feedback-based DVS scheme is further extended to be leakage aware, which considers not only dynamic but also static power consumption caused by leakage current in circuits. A combined DVS, delay and sleeping scheme is proposed for architectures where static power exceeds dynamic power in some cases. DVS is used when dynamic power dominates the total power consumption, while a sleep mode is entered when static power becomes dominant. The extended algorithm, DVSleak, shows 30% additional energy savings on average over a pure DVS algorithm in the simulation experiment.

#### Dynamic Voltage Scaling with Feedback EDF Scheduling for Real-time Embedded Systems

by

#### Yifan Zhu

A dissertation proposal submitted to the Graduate Faculty of North Carolina State University in partial satisfaction of the requirements for the Degree of Doctor of Philosophy

#### **Department of Computer Science**

Raleigh

2005

Approved By:

Dr. Robert Fornaro

Dr. Vincent W. Freeh

Dr. Frank Mueller Chair of Advisory Committee Dr. Douglas S. Reeves

#### Biography

Yifan Zhu was born in Hangzhou, a city on the east coast of China, and moved to the city of Wuhan when he was five. He pursued a Bachelor of Science degree in Computer Science from Huazhong University of Science and Technology at Wuhan, China in 1998. Upon completion of his undergraduate coursework, Yifan entered the graduate school at the same university and received a Master of Science degree in Computer Science in 2001. He came to North Carolina State University in the Fall of 2001. He is a research assistant at the Center for Embedded Systems Research (CESR). With the defense of this dissertation, he is receiving the Ph.D degree in Computer Science from North Carolina State University in August 2005.

#### Acknowledgements

I would like to express my gratitude to all those who gave me the possibility to complete this thesis. First, I would like to thank my adviser, Dr. Frank Mueller, for being a great mentor to me both personally and professionally. His suggestions and encouragement stimulated me all the time during the research and writing of this thesis. I also want to thank all the members in the embedded group for their support in my research work. Especially, I am obliged to Ajay Dudani for his contribution on our early work of the DVS research. I also want to thank Aravindh v. Anantaraman, Ali El-Haj Mahmoud and Rvai K. Venkatesan for their assistantship in an initial design and implementation of the DVS system on the IBM 405LP board. I would like to thank Bishop Brock from IBM, Austin for his valuable help on some of the technical details of the IBM experimental board.

I am also indebted to Dr. Douglas S. Reeves, Dr. Vincent W. Freeh and Dr. Robert Fornaro for serving on my dissertation committee and their valuable suggestions on this thesis.

Finally, but not least, I want to thank my parents and my girlfriend for their constant emotional support and good wishes during the odyssey of my Ph.D study.

# Contents

| List of Figures |                                         |                                                                                                                                                                                                                               | vi                                                                                           |

|-----------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| $\mathbf{Lis}$  | t of                                    | Tables                                                                                                                                                                                                                        | viii                                                                                         |

|                 | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4 | oduction         Dynamic Voltage Scaling         Motivation         Contributions         Dissertation Outline                                                                                                                | $     \begin{array}{c}       1 \\       3 \\       5 \\       6 \\       8     \end{array} $ |

|                 | <b>Rela</b><br>2.1<br>2.2<br>2.3        | Ated WorkDynamic Voltage ScalingFeedback Real-time SchedulingLeakage-aware DVS Scheduling                                                                                                                                     | <b>9</b><br>9<br>12<br>14                                                                    |

| -               | Feed<br>3.1<br>3.2                      | Iback-DVS FrameworkTask ModelArchitectural Framework                                                                                                                                                                          | <b>16</b><br>16<br>17                                                                        |

|                 | Volt<br>4.1<br>4.2<br>4.3<br>4.4        | age-Frequency SelectorTask SplittingStatic Slack UtilizationOynamic Slack PassingPreemption Handling                                                                                                                          | <b>19</b><br>20<br>21<br>22<br>24                                                            |

|                 | Feec<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | <b>Iback Controller</b> Basic PID Control         Proportional Feedback Control Design         Multi-input Control Design         Single-input Control Design         Stability Analysis of the Single-input Feedback Control | 27<br>27<br>29<br>30<br>32<br>33                                                             |

| 6  | Alg          | orithm and Its Correctness              | 35 |  |

|----|--------------|-----------------------------------------|----|--|

|    | 6.1          | Algorithm Description                   | 35 |  |

|    | 6.2          | Examples                                | 36 |  |

|    | 6.3          | Correctness of the Algorithm            | 40 |  |

| 7  | Sim          | ulation Experiments                     | 45 |  |

|    | 7.1          | Experimental Method                     | 45 |  |

|    | 7.2          | Results                                 | 48 |  |

|    | 7.3          | Summary                                 | 55 |  |

| 8  | Rea          | l Architecture Evaluation               | 56 |  |

|    | 8.1          | Platform and Methodology                | 56 |  |

|    | 8.2          | Synchronous vs. Asynchronous Switch     | 58 |  |

|    | 8.3          | DVS Scheduler Overhead                  | 60 |  |

|    | 8.4          | Impact of Different Workloads           | 63 |  |

|    | 8.5          | Comparison with Simulation Results      | 67 |  |

| 9  | Lea          | kage-Aware Feedback-DVS                 | 72 |  |

|    | 9.1          | Motivation                              | 72 |  |

|    | 9.2          | Power Model                             | 74 |  |

|    | 9.3          | DVSleak Algorithm                       | 75 |  |

|    |              | 9.3.1 Speed Reduction vs. Task Delaying | 78 |  |

|    |              | 9.3.2 Delay Policy                      | 79 |  |

|    | 9.4          | Simulation Experiment                   | 83 |  |

| 10 | Con          | clusion and Future Work                 | 91 |  |

| Bi | Bibliography |                                         |    |  |

# List of Figures

| 1.1          | Look-ahead RT-DVS Energy for Constant/Fluctuating Workload              | 5                                      |

|--------------|-------------------------------------------------------------------------|----------------------------------------|

| 3.1          | Feedback-DVS Framework                                                  | 17                                     |

| $4.1 \\ 4.2$ | Task Splitting                                                          | $\begin{array}{c} 20\\ 23 \end{array}$ |

| 4.3          | Future Slot Reservation                                                 | 25                                     |

| 6.1          | Discrete Scaling Levels for 3 Tasks                                     | 38                                     |

| 6.2          | Schedules: Simple and PID Feedback                                      | 39                                     |

| 6.3          | Delayed Start of Tasks due to Scaling                                   | 41                                     |

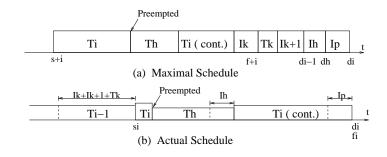

| 6.4          | Maximal vs. Actual Schedule                                             | 42                                     |

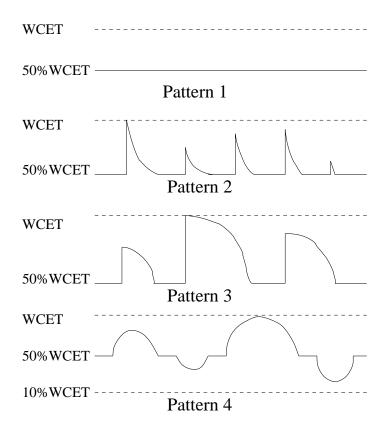

| 7.1          | Task Actual Execution Time Pattern                                      | 47                                     |

| 7.2          | Execution Time Pattern 1                                                | 49                                     |

| 7.3          | Execution Time Pattern 2                                                | 49                                     |

| 7.4          | Execution Time Pattern 3                                                | 50                                     |

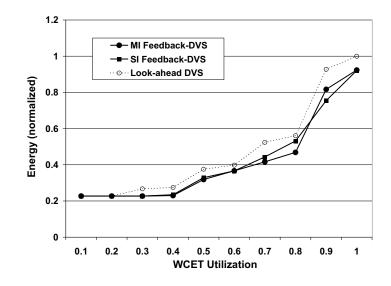

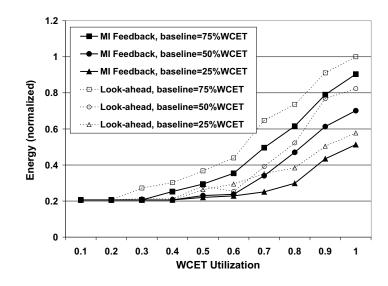

| 7.5          | Multi-input Feedback-DVS, Varying Baseline                              | 51                                     |

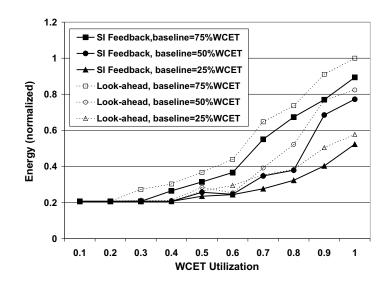

| 7.6          | Single-input Feedback-DVS, Varying Baseline                             | 51                                     |

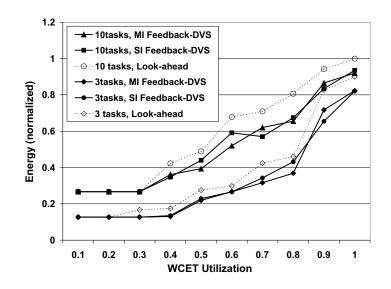

| 7.7          | 10-task vs. 3-task under Pattern 1                                      | 52                                     |

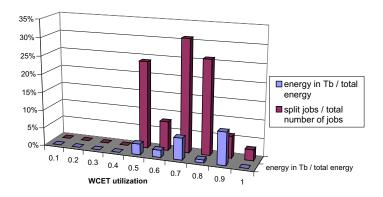

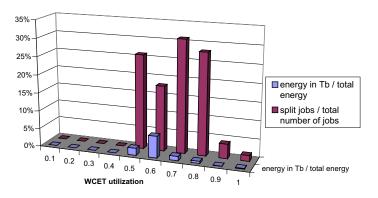

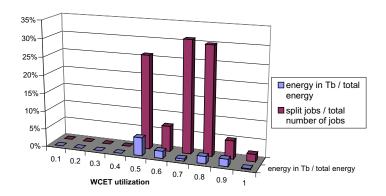

| 7.8          | Pattern 1, Percentage of subtask(energy) in $T_B$                       | 53                                     |

| 7.9          | Pattern 2, Percentage of subtask(energy) in $T_B$                       | 53                                     |

| 7.10         | Pattern 3, Percentage of subtask(energy) in $T_B$                       | 54                                     |

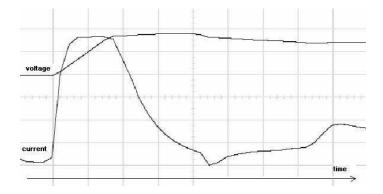

| 8.1          | Current and Voltage Transition During Asynchronous Frequency Switch-    |                                        |

|              | ing                                                                     | 58                                     |

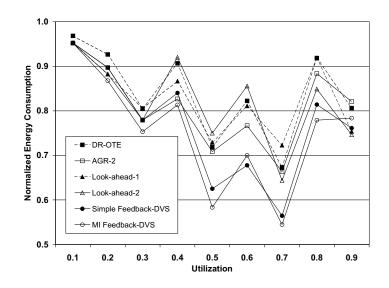

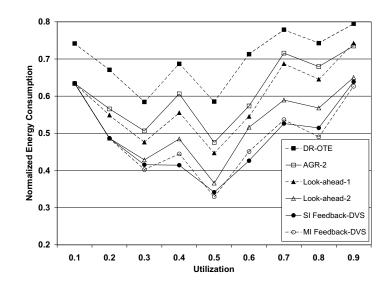

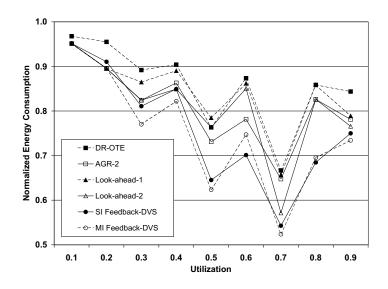

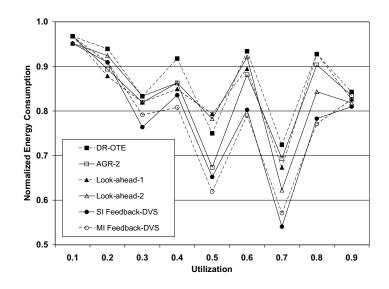

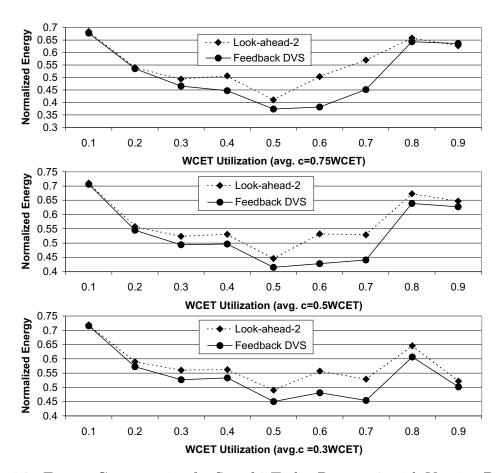

| 8.2          | Energy Consumption for Set of 3 Tasks, Pattern 1                        | 64                                     |

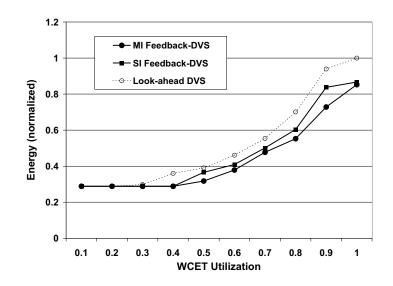

| 8.3          | Energy Consumption for Set of 3 Tasks, Pattern 2                        | 65                                     |

| 8.4          | Energy Consumption for Set of 3 Tasks, Pattern 3                        | 66                                     |

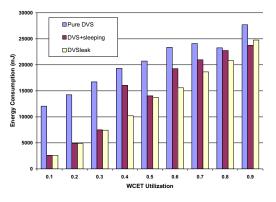

| 8.5          | Energy Consumption for Set of 3 Tasks, Pattern 4                        | 67                                     |

| 8.6          | Energy Consumption for Set of 30 Tasks, Pattern 2                       | 68                                     |

| 8.7          | Energy Consumption for Set of 3 Tasks, Pattern 4, with Varying Baseline | 69                                     |

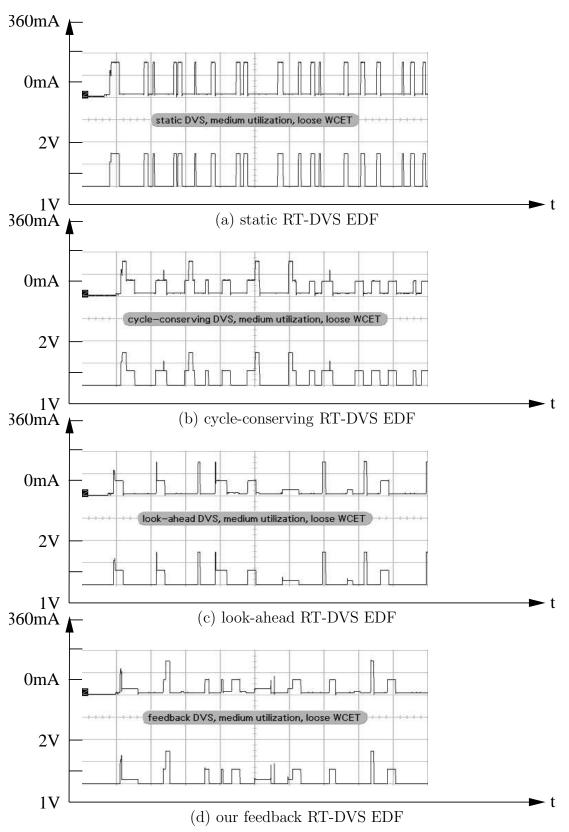

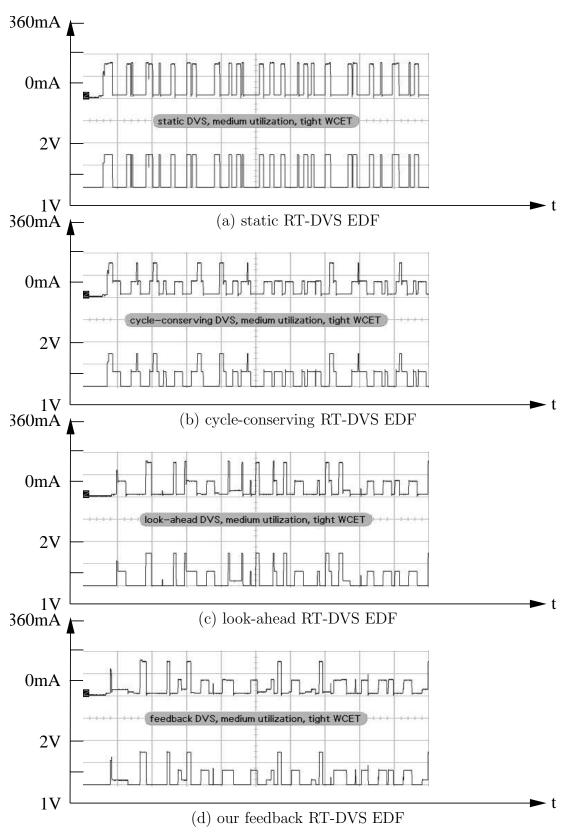

| 8.8 | Voltage/Current Oscilloscope Shot, Loose WCET= $2 \times$ ActualExec- |    |

|-----|-----------------------------------------------------------------------|----|

|     | Time, $U=0.5$                                                         | 70 |

| 8.9 | Voltage/Current Oscilloscope Shot, Tight WCET= ActualExecTime,        |    |

|     | U=0.5                                                                 | 71 |

| 9.1 | Combining DVS and Leakage Savings                                     | 77 |

| 9.2 | Speed Reduction vs. Task Delaying                                     | 78 |

| 9.3 | Delay vs. Non-delay                                                   | 80 |

| 9.4 | Rules for Task Delaying                                               | 81 |

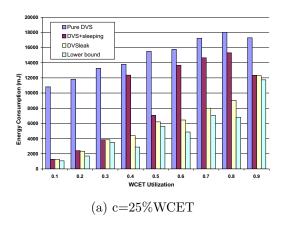

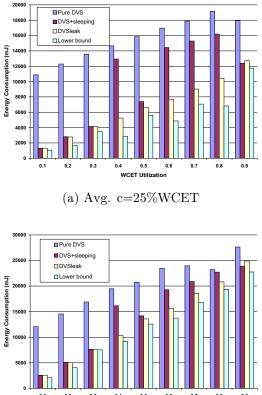

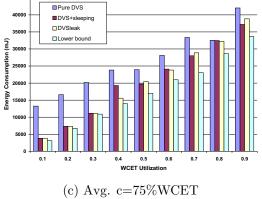

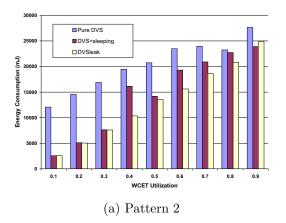

| 9.5 | Energy Savings for 3 Tasks, Pattern One under Different Actual Exe-   |    |

|     | cution Times (Constant) and Utilization                               | 85 |

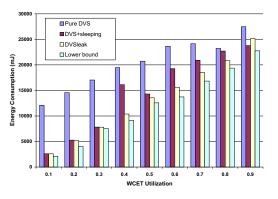

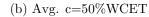

| 9.6 | Energy Savings for for 3 Tasks, Pattern Two under Different Actual    |    |

|     | Execution Times (Variable) and Utilization                            | 87 |

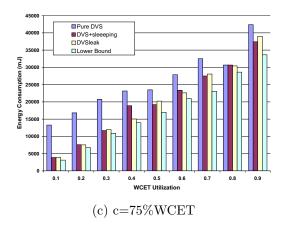

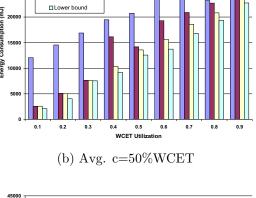

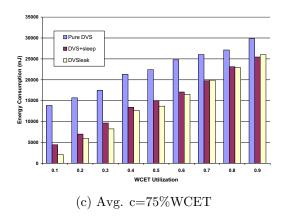

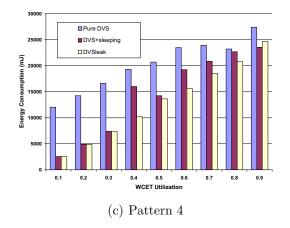

| 9.7 | Energy Savings for 10 Tasks, Pattern Two under Different Actual Ex-   |    |

|     | ecution Times (Variable) and Utilization                              | 88 |

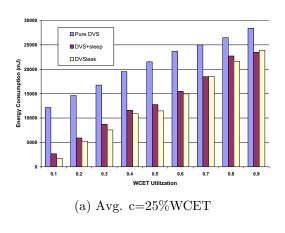

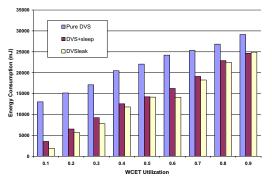

| 9.8 | Energy Savings for 3 Tasks, Dynamic Pattern $2/3/4$ when Average      |    |

|     | Execution Time = $50\%$ WCET $\ldots$                                 | 90 |

# List of Tables

| 6.1 | Sample Task Set                                      | 40 |

|-----|------------------------------------------------------|----|

| 7.1 | Processor Model for Scaling                          | 46 |

| 8.1 | Valid Frequency/Voltage Pairs                        | 57 |

| 8.2 | Frequency/Voltage Switch Overhead                    | 59 |

| 8.3 | Overhead of DVS-EDF Scheduler                        | 60 |

| 8.4 | Task Set                                             | 60 |

| 8.5 | Energy $[mW - hrs]$ consumption per RT-DVS algorithm | 61 |

# Chapter 1

# Introduction

Energy consumption is a major concern for today's computer systems. For generalpurpose systems, such as desktop servers or cluster computers, energy management is necessary due to operational cost and environment issues. For example, currently over 25% of the total operational cost comes from air conditioning, backup cooling and power delivery systems [48, 59]. The worldwide total power dissipation of desktop computer processors was 160 megawatts in 1992, which increased to 9000 megawatts in 2001 [66]. Sustained high power consumption produces excessive heat, which may cause failure of the CPU and other hardware components. Empirical data from two leading vendors indicates that the failure rate of a computer node doubles with every 10°C increase [9]. The total product cost also increases since more complex cooling and packaging designs are required to serve high energy systems. Intel estimates that more than \$1/W per CPU chip will be incurred if the CPU's power dissipation exceeds 35-40W [65].

For battery-powered embedded systems, efficient energy management is especially important. Examples of such devices include Web pads, advanced personal digital assistants (PDAs), cell phones and pocket PCs. Their peak performance demands could exceed 500 MIPS but the power consumption of the processor core during that peak activity should best be kept at or below 500mW [50]. Increasing battery capacity is one solution to this problem, although no dramatic breakthrough is foreseeable right now. Projected improvements in the capacity of batteries (5-10% annual growth rate) are much slower than what is needed to support ever-increasing processor power [31]. Therefore, it becomes an urgent challenge to cut energy consumption with efficient energy management schemes. Reducing power consumption can result in the same order of magnitude of energy savings as the improvement of battery technology itself.

The energy consumption problem can be approached from either the hardware perspective or the software perspective. From the hardware perspective, multiple power states are integrated into the micro-architecture level, the circuit level, and the device level. Some industry standards were developed, such as the Advanced Power management (APM) specification and the Advanced Configuration and Power Interface (ACPI). Today's major microprocessor manufacturers developed their own power management schemes in processor products, such as AMD's PowerNow technology, Intel's SpeedStep technology and Transmeta's LongRun technology. Lower power consumption also allows more densely packed circuits, resulting in higher speed and more affordable microprocessor chips. From the software perspective, energy management has traditionally focused on coarse-grained power shutdown strategies, which put the computer into a sleep or suspend state whenever the system is idle. Since the CPU sleep state requires a high-overhead shutdown and wake-up operation, it is not an available option in many situations. The sleep state also restricts system functionality, resulting in slower response time for external requests. In the absence of long idle periods in a system schedule, such a coarse-grained power management strategy becomes infeasible. More sophisticated approaches are required, which is one of the contributions of this thesis.

To study the power consumption problem, an appropriate power model is required. The following power dissipation model for CMOS-based processors is widely used [48]:

$$P \approx A C_L V_{dd}^2 f_{clk} + I_{leak} V_{dd} + P_{short} \tag{1.1}$$

where P is the power dissipation,  $V_{dd}$  is the voltage supply,  $f_{clk}$  is the clock frequency, A is the activity of the gates in the system, and  $C_L$  is the total capacitance seen by the gate outputs. The first component,  $AC_L V_{dd}^2 f_{clk}$ , is called dynamic power, which is the power consumption of charging and discharging the capacitive load on each gate's output. The second component,  $I_{leak}V_{dd}$ , is called static power or leakage power, which is caused by the leakage current in the circuit. The third component,  $P_{short}$ , is the short-circuit power, which reflects the power dissipation due to shortcircuit current. Among the three components, dynamic power is the dominant factor, while the other two can be ignored in most situations. This is the assumption of our research, although in later chapters of this dissertation we consider systems where the leakage power is dominant due to a trend toward lower threshold voltages.

Different solutions have been proposed to reduce the energy consumption of a CMOS-based processor based on Equation 1.1. They include circuit redesign, clock gating and dynamic voltage scaling [65]. Circuit redesign reduces the capacitance  $C_L$  by restructuring the logic. Clock gating partitions the circuit into different clock domains and turns different domains on or off according to their usage requirements. Dynamic voltage scaling lowers the supply voltage  $V_{dd}$  and clock frequency  $f_{clk}$  to reduce the dynamic power of the processor. Because of the quadratic relationship between the supply voltage and power consumption, dynamic voltage scaling can result in significant power reduction for processors.

#### 1.1 Dynamic Voltage Scaling

Dynamic voltage scaling (DVS) and dynamic frequency scaling (DFS) are mechanisms that dynamically change the voltage and frequency of a processor to reduce its energy consumption. DVS and DFS are usually combined together because reduced voltage also limits the maximum clock frequency,  $f_{max}$ , as shown in the following:

$$f_{max} \propto (V_{dd} - V_t) / V_{dd} \tag{1.2}$$

In this dissertation, we use DVS to refer to both dynamic voltage scaling and dynamic frequency scaling. Processors with DVS functionalities provide special control registers to determine the CPU clock frequency and supply voltage. Software updates these registers dynamically during program execution to change the CPU frequency and voltage. Although this feature is provided by hardware, it is the software which decides when and how to adjust the frequency and voltage.

In contrast to previous coarse-grained energy saving solutions such as turning off processors or I/O devices, DVS is a fine-grained energy saving mechanism. Frequency and voltage scaling incur much less performance overhead than processor shutdown operations. Therefore, it is possible to exploit aggressive power management policies for DVS algorithms.

We study task-based DVS algorithms for hard real-time systems in this dissertation. DVS algorithms can be either interval-based or task-based. Interval-based approaches divide the time into fixed-length intervals. DVS operation is activated only at the beginning of each interval. Interval-based schemes are mostly used in generalpurpose systems with mixed workloads. However, interval-based DVS schemes are not suitable for real-time systems where each task has its own timing requirement. For example, in a periodic real-time task model, each task is described by its period (P), deadline (d), and worst-case execution time (WCET). A violation of such timing requirements results in either performance degradation for soft real-time systems, or even serious consequences for hard real-time systems. Interval-based DVS schemes do not take this per-task timing information into consideration. Deadline misses cannot be detected until the start of the next interval. A task-based DVS approach, however, adjusts CPU frequency and voltage on a per-task basis instead of at a fixed time interval. DVS functionality is integrated into operating system schedulers so that it can be activated each time a task is dispatched or completed. Therefore, a task-based DVS scheme is a better solution to real-time systems than an interval-based DVS scheme.

Real-time systems bring new opportunities as well as new challenges to DVS algorithms. On one hand, powerful processors are often used in real-time systems to meet the worst-case execution demands, although these demands rarely occur in practice. System utilization is often kept at a low level to ensure operational safety, which creates the opportunity for DVS schemes to reduce CPU frequency. On the other hand, real-time systems expose a fundamental trade-off between energy consumption and timing requirements. Reducing the CPU frequency results in a slower computing speed. A specific operation may consume less power on average but take longer to complete. DVS algorithms need to guarantee that the timing requirements of tasks are maintained. Power consumption is reduced while continuous system services and quick response times are still available. In addition, frequency or voltage switching overhead may cancel out the benefits of DVS schemes. Deploying DVS intensively may influence the timing behavior of the system and actually result in more energy consumption. All these issues must be considered during the design of a DVS algorithm for real-time systems.

#### 1.2 Motivation

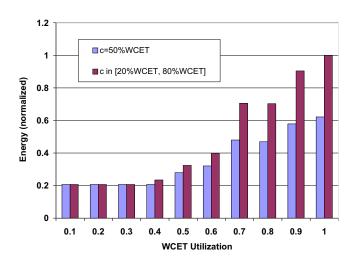

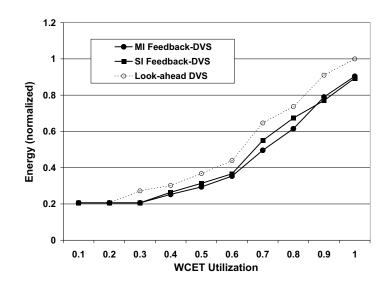

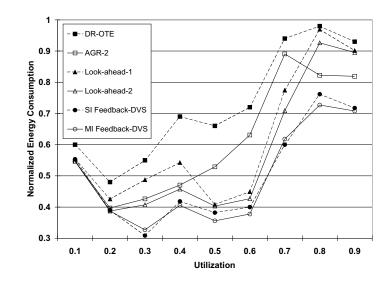

Figure 1.1: Look-ahead RT-DVS Energy for Constant/Fluctuating Workload

The potential to save energy by combining DVS techniques with operating system scheduling has been investigated in previous work. Significant savings have been reported for general-purpose computing systems [13, 16, 30, 40, 52, 69, 55, 15] as well as real-time systems [19, 20, 32, 63, 53, 10, 47, 14, 2, 29]. DVS algorithms for general-purpose systems often use various heuristics to reduce processor voltage or frequency according to the observed system workload [69, 52, 13]. DVS for hard real-time systems, in contrast, requires more subtle control. Timing requirements must be considered by the DVS algorithms to determine the processor frequency.

Traditionally, hard real-time scheduling relies on a priori knowledge of the worst-

case execution time (WCET) of a task to guarantee the schedulability of the system. A safe upper bound on the WCET of a task can be provided through static analysis, dynamic analysis or a combination of both [56, 51, 17, 73, 37, 18, 1, 35, 36, 12, 49, 68]. Prior experiments have shown a wide variation between longest and shortest execution times for many actual applications. For example, actual execution times of real-world embedded tasks are observed to vary by as much as 87% relative to their measured WCET [68]. Budgeting for the WCET may result in excessive energy consumption even though actual utilization is lower than the worst case.

Also, pure DVS techniques do not perform well for dynamic systems where the system workloads vary significantly. Many of the existing hard real-time DVS schemes are not able to adapt well to dynamically changing workloads. For example, we compared the energy consumption of Look-ahead RT-DVS [53] between a constant workload and a fluctuating workload, as depicted in Figure 1.1. Both workloads contain three periodic tasks defined as  $T_1=\{3,8\}, T_2=\{3,10\}$  and  $T_3=\{1,14\}$ , where  $T_i=\{WCET,Period\}$  for i = 1...3. The constant workload consists of tasks whose actual execution times (denoted by c) among different jobs are 50% of their WCET. The fluctuating workload consists of tasks with an average execution time of 50% WCET. Their actual execution times fluctuate between 20% and 80% of their WCET (following variation patterns similar to Figure 7.1, discussed later). Figure 1.1 demonstrates that, in the worst case, Look-ahead RT-DVS degrades up to 40% for the fluctuating workload. More adaptable DVS schemes are required for these workloads with dynamic changing execution times.

#### **1.3** Contributions

In this thesis, we develop and evaluate a novel DVS technique for dynamic workloads, considering practical design and implementation issues. The novel contributions of this thesis over previous work include:

• A feedback-based DVS framework for dynamic workloads with hard real-time requirements. A feedback controller is integrated into the DVS scheduler to

achieve better adaptivity for dynamic task sets with fluctuating execution times. The speed of the processor is adjusted dynamically by the operating system. The feedback technique enables the system to select the appropriate frequency and voltage settings so that energy consumption is significantly reduced. It also helps guarantee the timing requirements of hard real-time tasks so that deadlines are not missed. Different feedback control structures are evaluated in our implementation. To the best of our knowledge, this is the first study of feedback control techniques exploiting DVS for hard real-time systems.

- A combined intra-task and inter-task DVS scheme. In contrast to compilerdirected intra-task DVS algorithms where the speed of a task is changed multiple times during program execution, the combined intra-task and inter-task DVS scheme presented in our work divides the execution budget of a task into at most two portions. Keeping the first portion at a low speed makes our algorithm more aggressive than a pure inter-task DVS algorithm. Changing the speed at most once for each task incurs lower overhead than that of a pure intra-task DVS algorithm.

- Slack passing and preemption-handling schemes for DVS schedulers. These schemes ensure the timing requirements of hard real-time tasks. They follow a greedy policy by passing as much slack as possible to scale the next running task. It speculates on the early completion of each task to aggregate unused slack for other tasks. When preemption occurs, the preempted task relinquishes its remaining slack and passes it on to the next task, while reserving enough slack in the future to avoid deadline misses. Different slack reservation schemes are studied to ensure the schedulability of the system.

- The implementation of our feedback DVS scheme in simulation, as well as the evaluation on a real embedded platform. For task sets with different dynamic execution time patterns, simulation experiments demonstrate the benefits of this scheme with energy savings of up to 29% over previous work. The evaluation on an embedded platform exhibits up to 24% additional energy savings over

other DVS algorithms. The comparison of synchronous and asynchronous DVS switching shows that the energy saving under asynchronous switching is not as significant as expected. The experimental results reveal that the  $V^2 f$  power model (Equation 1.1) works well for DVS performance analysis.

• An extension of the feedback-DVS scheme to embedded architectures where the dynamic power is not dominant. An combined DVS and leakage control scheme is presented to save both static and dynamic power. It automatically alternates between a voltage-scaling mode and a processor sleep mode, according to the execution scenario of tasks. Simulation experiments show that the combined DVS and leakage control scheme saves 15% additional energy on average over a pure sleep policy and 30% additional energy on average over a pure DVS algorithm.

#### **1.4** Dissertation Outline

The remaining chapters are structured as follows. In Chapter 2 we present related work. Chapter 3 gives an overview of the proposed feedback-DVS framework. We describe in detail the voltage-frequency selector in Chapter 4, and the feedback controller in Chapter 5. Chapter 6 gives an algorithmic description of the DVS framework, as well as some examples. Chapter 7 presents simulation results to demonstrate the performance of our feedback-DVS scheme under different workload conditions. Chapter 8 evaluates our algorithm on an embedded platform. Chapter 9 discusses the leakage power issue and proposes a leakage-aware DVS scheme. Chapter 10 summarizes this research and indicates future work.

# Chapter 2

# **Related Work**

The proposed feedback-DVS frame combines feedback real-time control with dynamic voltage scaling techniques. In this chapter we describe some of the related research work.

#### 2.1 Dynamic Voltage Scaling

Dynamic voltage scaling has been studied by many researchers for general-purpose systems as well as real-time embedded systems. DVS for general-purpose systems is different from DVS for real-time systems. On one hand, general-purpose systems do not need to maintain any workload timing requirements, which have to be guaranteed by real-time systems. On the other hand, general-purpose systems have no knowledge of the system's worst-case behavior, which is usually available in real-time systems.

A DVS algorithm can be either on-line or off-line. On-line algorithms assign the processor frequency at run-time according to the dynamic state of the system. Offline algorithms determine the processor frequency statically, before the execution of the system.

Weiser *et al.* [69] and Govil *et al.* [13] are among the first researchers who propose DVS algorithms in operating systems. In 1994, Weiser *et al.* first proposed an interval-based DVS algorithm to monitor CPU utilization constantly on a generalpurpose operating system. Processor frequency and voltage are adjusted at the beginning of each interval according to the CPU utilization of previous execution traces. Govil *et al.* compared a number of DVS policies in a simulation environment. Their work suggested that a simple smoothing algorithm was better than a more complex algorithm. Since then, DVS strategies were further evaluated and extended by Pering *et al.* [52] and Grunwald *et al.* [16]. Pering *et al.* examined DVS algorithms through trace-driven simulation. Grunwald *et al.* evaluated DVS policies through physical measurements. Chandrasena *et al.* [7] incorporated the strengths of the conventional workload averaging technique and the rate selection algorithm. System workloads are buffered to estimate the CPU rate until the scaling factor matches the system quantized rates. Saputra *et al.* [61] presented off-line compiler-directed DVS algorithms based on integer linear programming to accommodate energy and performance constraints.

The optimality of DVS algorithms is also studied in some of the previous work. Ishihara et al. [24] proved that on a processor with a small number of discrete variable voltages the energy consumption is minimized when the schedule contains at most two voltage levels. The two-speed schedule is only optimal when a task's actual execution time can be determined statically, which is in practice not possible. When actual execution time varies from instance to instance, a multiple-speed schedule can result in lower energy than a dual-speed schedule. On an ideal processor with continuous voltage and frequency levels, the energy consumption is minimized when the task runs at a constant speed and completes exactly before its deadline. This optimality has also been mentioned by Weiser et al. [69] and Lorch et al. [40], and been formally proved by Yao et al. [71] and Ishihara et al. [24]. Qu [57] presented the optimality of a DVS algorithm using a more realistic model where the voltage and frequency switching overhead are considered. When the system's workload requirement is known only probabilistically. Lorch and Smith [40] showed that a constant speed is not optimal anymore. Instead, the energy is expected to be minimized by gradually increasing the CPU frequency as the task progresses. Xie *et al.* [70] explored opportunities and limits of compile-time DVS scheduling. A mixed integer linear program formulation is used to analyze the potential of compiler-directed DVS algorithms. One important result of their work is that as the number of available voltage levels increase, the energy savings decrease significantly. Saewong *et al.* [60] proposed a series of voltage scaling schemes targeting different hardware configurations and task set characteristics. Their results show that some non-optimal schemes may be more suitable than optimal schemes when the system has a high voltage scaling overhead.

When DVS algorithms are applied to real-time systems, timing requirements of real-time applications pose additional challenges. Lee *et al.* [33] presented a branchand-bound algorithm to determine statically the operating frequency of real-time task sets. Due to the complexity of the algorithm, only two frequency levels are assumed in their model. The algorithm proposed by Liu *et al.* [39] derives optimal speed functions between an upper bound and a lower bound of processor cycles. Their online algorithm reclaims unused execution cycles to further reduce energy consumption. Pillai and Shin [53] proposed a set of dynamic DVS algorithms based on traditional hard real-time mechanisms, namely rate-monotone scheduling and earliest-deadlinefirst scheduling. They extended the schedulability test of RM and EDF algorithms to incorporate CPU frequency scaling. Static DVS, cycle conservative DVS, and lookahead DVS are presented. Look-ahead DVS is the most aggressive DVS scheme among the suite of algorithms proposed. Unlike our algorithm which applies frequency scaling to only the current task, they assumed a unified frequency scaling factor on all tasks. In their most aggressive variant, the look-ahead technique is used to achieve extensive energy savings by deferring as much work as possible. However, the frequency value obtained in their algorithm is not always the lowest possible frequency for a single task, as shown by Dudani *et al.* [11].

Some of the other aggressive real-time DVS schemes exploit early completion of task executions based on statistical information of the workload under dynamic scheduling [2] or static priority scheduling [14]. Aydin *et al.* discuss a series of algorithms, which dynamically reclaim unused computation time of real-time tasks to reduce the processor speed [4]. Energy-aware scheduling of hybrid workloads, including both periodic and aperiodic tasks, are further investigated by Aydin and Yang [3]. Their algorithm is based on early completion of tasks and collects idle time up to the next task's activation. We exploit both the idle time prior to the next task's activation as well as any idle slots up to the deadline of the task in the maximal schedule.

The idea of deriving a feasible dual-level DVS schedule from an ideal case was first proposed by Gruian [14, 15]. It combines off-line and on-line scheduling at both task level and task-set level. Stochastic data derived from previous task execution traces are used to produce energy-efficient schedules. Multiple frequency levels may be assigned to a single task. Our approach, instead, assigns at most two different frequencies for each task. Our algorithm targets dynamic-priority scheduling while Gruian restricts his approach to fixed-priority scheduling. Dual-speed scheduling was also investigated by others. Zhang et al. vary the processor speed between high and low whenever non-preemption blocking occurs [72]. Lee *et al.* assume an architecture where only two physical speed levels exist [33]. Our approach considers a more general case where multiple frequency and voltage levels are chosen by subsequent jobs of the same task or even different tasks. Jejurikar and Gupta investigate static and dynamic slowdown factors for periodic tasks [26] and combine them with procrastination scheduling [27] and preemption threshold scheduling [25]. Several of these algorithms were compared in a unified simulation environment, SimDVS [62]. In contrast, we measure power consumption on a concrete micro-architecture for several EDF-based algorithms.

Last-chance scheduling without energy considerations goes back to Chetto *et al.* [8]. We apply their philosophy in a DVS context. We develop a novel DVS variant based on task splitting with exactly two parts. Such a dual-speed approach aggressively reduces power consumption if the first subtask is fully utilized while the second subtask never executes. Our feedback approach triggers this behavior, which is superior to Gruian's step-wise increase of frequencies with a stochastic approach.

#### 2.2 Feedback Real-time Scheduling

There have been a number of efforts of applying feedback techniques on generalpurpose control systems. Only recently did researchers begin to incorporate feedback control to real-time scheduling theory [41, 42]. Feedback control for real-time scheduling was first investigated by Stankovic *et al.* [64]. Real-time system performance specifications are analyzed systematically through a control-theoretical method. Lu et al. [42] further proposed a feedback control real-time scheduling framework for unpredictable dynamic real-time systems where task execution times diverge from their worst case . Real-time system performance specifications are analyzed and satisfied systematically through a control-theory based methodology. Dynamic models of realtime systems are developed to identify different categories of real-time applications. While their feedback control framework is for general purpose real-time scheduling, our scheme focuses on feedback control schemes for reducing energy consumption of processors.

For multimedia systems, a formal feedback control algorithm combined with dynamic voltage/frequency scaling technologies was first described by Lu *et al.* [43]. Both continuous and discrete DVS settings are exploited in their scheme to reduce energy consumption. An adaptive set-point is used to achieve fast responses with a stable multimedia throughput.

PID-Feedback control was also proposed for energy-aware computing in previous work. Varma *et al.* [67] presented a feedback-control algorithm where the previous workload execution history is used to predict the future workload behavior by a discrete-time PID function. The combination of the proportional, integral and derivative parts of the PID function provides appropriate estimation across different applications. Poellabauer *et al.* [54] applied a feedback loop on cache miss rates to make more reliable predictions of future task behavior. A general energy management scheme with feedback control was proposed by Minerick *et al.* [46]. An average energy usage is achieved by continuously adjusting the frequency of a processor to meet the energy consumption goal. A PI (proportional and integral) feedback controller is used to change the CPU frequency based on previous energy consumption. While Varma, Lu and Poellabauer's work target soft real-time systems and Minerick's work targets general purpose systems, our feedback DVS scheme focuses on hard real-time systems where timing constraints must not be violated.

#### 2.3 Leakage-aware DVS Scheduling

Static power consumption caused by leakage current has incurred much attention in recent years. Conventional DVS scheduling strategies are modified to be leakageaware. Lee *et al.* [34] proposed greedy methods to maximize the duration of idle and busy periods based on the worst-case execution time [34]. Their algorithms are integrated into conventional dynamic priority scheduling and fixed priority scheduling policies. It is most useful if there are many relatively short inter-task idle periods that can be grouped together. Since actual execution times often diverge considerably from WCET, a conceptual busy period is interspersed with dynamic slack due to early completion of tasks.

Quan *et al.* described an enhanced DVS algorithm to reduce both dynamic and static power consumption [58]. The latest release time of each job in the task set is computed off-line and subsequently used by an on-line scheduler. Their approach is based on fixed-priority scheduling while ours is based on dynamic-priority scheduling. Their online scheduler always delays the release time of a task to its latest start time (last chance) as long as the processor is idle. Such an aggressive scheme is not always the most energy efficient solution. In our algorithm, we make delay decisions based upon the actual execution time of tasks *via* feedback, which is more energy efficient on average.

Jejurikar *at al.* enhanced EDF scheduling with a procrastination algorithm [28]. A delay interval is calculated for each task, which only considers static task information and may result in a pessimistic schedule. Our scheme is integrated with the online scheduler. It converts dynamic slack, generated due to the critical speed threshold or the early completion of tasks, into idle or sleep time. Their approach also assumes that a power manager, implemented as a controller in hardware, handles interrupts and timers when new tasks are released. In contrast, our scheme does not require any special hardware support except for DVS and sleep modes.

Zhang *et al.* presented a compiler-supported solution to reduce leakage energy consumption [74]. Data-flow analysis is employed to identify basic blocks that do not utilize certain functional units. Those functional units are temporarily deacti-

vated by compiler-generated software instructions. While their solution targets microarchitectural effects inside a processor, our approach puts the processor and *all* of its resources into the sleep mode.

## Chapter 3

# **Feedback-DVS Framework**

In this chapter, we first define the task model used throughout this work. The architecture of the feedback-DVS framework is then described in detail for a better understanding of the scheme.

#### 3.1 Task Model

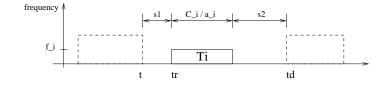

We use a periodic, fully preemptive and independent real-time task model [38] in our framework. Each task  $T_i$  is defined by a triple  $(P_i, D_i, C_i)$ , where  $P_i$  is the period of  $T_i$ ,  $D_i$  is the relative deadline of  $T_i$ , and  $C_i$  is the worst-case execution time (WCET) of  $T_i$ , measured at the maximal processor frequency. We always assume  $D_i=P_i$  in our model. The periodically released instances of a task are called jobs.  $T_{ij}$  is used to denote the  $j^{th}$  job of task  $T_i$ . Its release time is  $P_i * (j - 1)$  and its relative deadline is  $P_i * j$ . We use  $c_{ij}$  to represent the actual execution time of job  $T_{ij}$ . Different instances of a task  $T_i$  usually has different actual execution times, which are always bounded by that task's worst case execution time  $C_i$ . The hyperperiod H of the task set is the least common multiplier (LCM) among the tasks' periods.

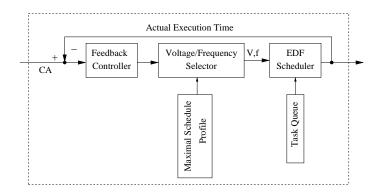

Figure 3.1: Feedback-DVS Framework

#### **3.2** Architectural Framework

Prior research on DVS for hard real-time system was primarily concerned with guaranteeing the schedulability of the task sets while energy consumption is minimized. But in a dynamic real-time environment where the task execution time varies significantly from job to job, a DVS scheduler should be able to adapt to the everchanging workloads as fast as possible. One important performance metric of such a system is how fast the DVS scheme can adjust the processor speed according to different workloads so that energy consumption is significantly reduced. To address this issue, we propose a framework called feedback dynamic voltage scaling (feedback-DVS). In this framework, we consider the scheduling problem in hard real-time systems with the earliest deadline first (EDF) policy. This framework is based on feedback control that incrementally corrects system behavior to achieve its energy objective, while the hard real-time timing requirements are still preserved. We assume that the processor can operate at several discrete voltage/frequency levels, which reflects contemporary processor technology with support for DVS. When there is no task running on the processor, the processor enters an idle state at a particular voltage/frequency level, usually the lowest voltage/frequency level on that processor.

Figure 3.1 depicts the framework of our feedback-DVS scheme. It consists of a feedback controller, a voltage-frequency selector, and an EDF scheduler. The feedback controller calculates the error from the difference between the actual execution time

of a job and  $C_i^A$ , the execution time of the first portion of that job (detailed in the task-splitting scheme in the next chapter). The voltage-frequency selector chooses a voltage/frequency level according to the error and the maximal schedule profile. The error is used to adjust the estimation of the execution time for the next job. The maximal schedule profile includes a running scenario of the task set from start time 0 to the end of a hyperperiod. It is generated offline assuming each job's actual execution time always equals the task's worst-case execution time. The voltage-frequency selector uses the information in the maximal schedule profile to choose an appropriate voltage-frequency level without causing any deadline misses. As long as a voltage/frequency level is determined, the EDF scheduler dispatches the ready task at that processor speed. Tasks are scheduled according to EDF policy, *i.e.*, the task with the earliest deadline is given the highest priority. The actual execution time of each job is used by the feedback controller to determine the frequency and voltage for successive jobs. The next two chapters detail the mechanism of the voltage-frequency selector and the feedback controller in the feedback-DVS frame.

## Chapter 4

# **Voltage-Frequency Selector**

The voltage-frequency selector is responsible for selecting a voltage-frequency pair each time a task is scheduled. Since power consumption increases proportionally to processor frequency and the square of the voltage [24], minimal energy consumption is obtained by running every task at a uniform processor speed. This is only a statically optimal solution. In a dynamic environment where a task's actual execution time is unknown until the task completes, it is not possible to derive the optimal uniform speed in advance. Our objective is to approximate a close-to-optimal solution by monitoring the actual execution time of each job. The start point of our scheme is the following inequality, which is a modification of the standard EDF [38] schedulability test:

$$\alpha^{-1}\frac{C_k}{P_k} + \sum_{i \in \{1,\dots,n\} \setminus \{k\}} \frac{C_i}{P_i} \le 1$$

$$(4.1)$$

Here,  $\alpha$  is a scaling factor defined as the ratio of the current processor frequency to the maximal available frequency, *i.e.*,  $\alpha = f_k/f_m$ . Instead of scaling at a single speed for all tasks, only the highest priority task (the task with the earliest deadline under EDF) is scaled. All remaining tasks are modeled to execute at the maximum frequency  $f_m$  in the future with a scaling factor of 1. The motivation of scaling only the current task is to anticipate a near-optimal solution using a greedy scheme. In the following, we explain in detail the speed setting scheme used in our voltage-frequency

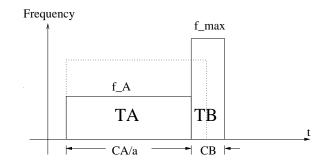

Figure 4.1: Task Splitting

selector.

#### 4.1 Task Splitting

For each task, the scaling factor  $\alpha$  depends on the total available slack when the task is scheduled. For example, at time 0, the available slack for the first task  $T_1$ is derived from the expression 4.1 as  $P_1(1 - \sum_{i=2}^n \frac{C_i}{P_i})$ . Its  $\alpha$  value is calculated as:  $\alpha = \frac{C_1}{P_1(1-\sum_{i=2}^n \frac{C_i}{P_i})}$ . In order to obtain an even lower speed for each task  $T_k$  and to make feedback control available for hard real-time systems, our scheme goes beyond that by splitting each task into two subtasks  $T_A$  and  $T_B$ . These two subtasks are allowed to execute at different frequency and voltage levels. As shown in Figure 4.1,  $T_B$  always executes at the maximum frequency level  $f_m$ , while  $T_A$  is able to execute at a lower frequency level than the level without task splitting. We expect that a task can finish its actual execution within  $T_A$  while reserving enough time in  $T_B$  to meet its deadline. We can safely scale the frequency of  $T_A$  using available slack before  $T_B$ executes at the maximum frequency following a last-chance approach [8]. In the next section, we can also see that such a task splitting scheme is necessary for applying feedback control on hard real-time systems. By splitting each task into at most two subtasks, we incur at most one speed change to each task and therefore keep the impact of voltage and frequency switching overhead to a minimum. Task splitting is transparent to users. It can be implemented as a timer handler. The timer is set up upon the dispatch of  $T_A$  and triggered at the end of  $T_A$ . If the task completes within  $T_A$  or a preemption occurs, the timer can be canceled and no additional overhead will be incurred. Only if execution cannot complete in  $T_A$  will the timer go off and trigger the DVS operation to enter the  $T_B$  sub-task.

Let  $C_k$ ,  $C_k^A$  and  $C_k^B$  be the worst-case execution cycles of task  $T_k$  and its two subtasks,  $T_A$  and  $T_B$ . Let  $s_k$  be the slack available to  $T_k$  when  $T_k$  is scheduled. We have:

$$C_{k} = C_{k}^{A} + C_{k}^{B}, \frac{C_{k}^{A}}{\alpha} + C_{k}^{B} = C_{k} + s_{k}$$

(4.2)

we derive  $\alpha$  from the above equation:

$$\alpha = \frac{C_k^A}{C_k^A + s_k} \tag{4.3}$$

Equation 4.3 shows that when task splitting is used, the scaling factor  $\alpha$  depends not only on the amount of available slack  $(s_k)$ , but also on the number of execution cycles assigned to  $T_A$ . In the following, we describe the methods used to determine these two values.

#### 4.2 Static Slack Utilization

The type of slack available during the scheduling of a real-time system falls into two categories. One is static slack due to under-utilized system workloads. The other one is dynamic slack due to early completion of tasks. In order to exploit these two types of slack, we consider an actual schedule and a maximal schedule. The maximal, schedule, or *worst-case* schedule, is the schedule produced by a standard EDF algorithm when the execution time of each job equals its WCET. The actual schedule is the actual execution scenario produced by our feedback-DVS algorithm where the execution time of each task varies from job to job. The maximal schedule is constructed offline in O(N) complexity, where N is the total number of jobs executed in a hyperperiod H. The static slack is exploited by adding an idle task,  $T_{n+1}$ , into the original task set to fill the gap between the actual utilization and 100% utilization. The idle task distributes the static slack throughout the entire hyper-period. Hence, static slack is not monopolized by a single task but evenly distributed. This also facilitates the online computation of static slack. The idle task has a non-zero WCET but its actual execution time is always zero. The WCET and the period of the idle task are chosen in such a way that the total utilization of the new task set becomes 100%. In other words,

$$P_{n+1} = P_1, C_{n+1} = P_{n+1}(1-U), c_{n+1} = 0.$$

(4.4)

Notice that any other choice of idle task periods is also legal. Most notably, the shortest period of any task,  $P_1$ , and the longest one,  $P_n$ , are interesting choices. We consider these options since they affect the amount of static slack available for other tasks. We choose the shortest period as the idle task's period to ensure that there is at least one idle task being released between any task's invocation to provide static slack for that task. The total static slack generated by idle task  $T_{n+1}$  in the interval [t1..t2] is denoted by:

$$idle(t1...t2) = \sum_{\substack{t1..t2}} idle \ slots \tag{4.5}$$

#### 4.3 Dynamic Slack Passing

Dynamic slack passing is a technique to reduce the online complexity of slack computation. It is based on the observation that slack generated by one job is usually not exhausted when the job completes. Instead of computing each job's slack from scratch, the previous job passes its unused amount of slack to the next job. That slack is further augmented by any static idle slots between the deadline of the previous job and the next job.

When there is no preemption, we express dynamic slack passing in terms of the release time  $r_{ij}$  of a task  $T_{ij}$  in the actual schedule, the initiation time  $I_{pk}$ , and the worst case completion time  $F_{pk}$  of the immediately previous task  $T_{pk}$  in the maximal schedule. The slack  $s_{ij}$  available to  $T_{ij}$  is defined as:

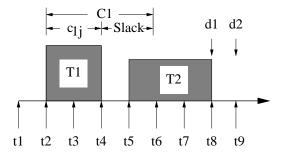

Figure 4.2: Dynamic Slack Passing

$$s_{ij} = \begin{cases} C_p - c_{pk} & \text{if } r_{ij} \le I_{pk} + c_{pk} \\ F_{pk} - r_{ij} & \text{if } I_{pk} + c_{pk} < r_{ij} < F_{pk} \\ 0 & \text{if } r_{ij} \ge F_{pk} \end{cases}$$

(4.6)

An example is depicted in Figure 4.2. Let task  $T_1$  with WCET  $C_1$  and deadline t8 execute its  $j^{th}$  job with an actual execution time of  $c_{1j}$ . Assume that when  $T_1$  is invoked at time t2, it inherits a total slack of S from its previous tasks.  $T_1$  is then scaled to a lower frequency with that slack and completes at time t4. The difference between  $C_1$  and  $c_{1j}$  is the new slack dynamically generated by  $T_1$ . So the total slack available at t5 is  $S = S + C_1 - c_{1j}$ . Note that the actual execution time  $c_{1j}$  may be less than, equal to, or greater than the worst-case execution time  $C_1$  because of task scaling. If  $C_1 > c_{1j}$ , Equation 4.6 just adds the slack produced by the early completion of  $T_1$  into the total slack. If  $C_1 < c_{1j}$ , Equation 4.6, in fact, reduces the total slack because  $c_{1j}$  exceeds its WCET in the maximal schedule (it is feasible under DVS as long as the available slack is not exceeded). The adjusted total slack is passed in full or in part to the next task  $T_2$  depending on  $T_2$ 's release time and deadline. Slack beyond  $T_2$ 's release time and deadline cannot be used by  $T_2$  and, therefore, will not be passed on to it.

When task preemption exists in the schedule, slack passing is handled specially. In the next section, we derive formulas to compute the slack for a preempted task.

#### 4.4 Preemption Handling

Preemption handling follows a greedy scheme in that we try to pass as much slack as possible to scale the running task. We speculate on its early completion to aggregate more slack for other tasks. When preemption occurs, the preempted task relinquishes its remaining slack and pass it on to the next task, just as it does when a task completes. But there are two differences here. First, the preempted task itself cannot generate any slack based on its own execution at the preemption point since the task's completion time is unknown. Hence, no additional slack is added to its inherited total slack. Second, the preempted task still needs some time to complete its execution in the future. The remaining execution time must be reserved in advance to avoid future deadline misses caused by over-exploiting slack from other tasks. At the preemption point, the expected remaining execution time,  $L_{ij}$ , of the preempted task is:

$$L_{ij} = C_i - c_{ij} \times \alpha^{-1} \tag{4.7}$$

where  $c_{ij}$  is the actual execution time up to the preemption point. Our slack passing scheme promises that the preempted task will not miss its deadline by reserving the expected remaining execution time from its slack:

$$s_{k,r} = s_k - L_{ij} \qquad (future \ slots) \tag{4.8}$$

where  $s_k$  is derived from Equation 4.6 and the resulting slack  $s_{k,r}$  is passed to the next task.

Future slot allocation is essential to ensure the feasibility of the schedule under DVS. Future slots will be allocated only if the maximal schedule does not have sufficient slots for the preempted job between the preemption point and the job's deadline. We devise multiple schemes for reserving these slots.

• Forward sweep: When a task T1 is preempted and requires  $L_{1j}$  slots in the future, the preempting task, T2, deducts this amount from its available slack s. If  $L_{1j} > s$ , T2 remains without slack. If another task T3 is initiated, the calculation repeats itself.

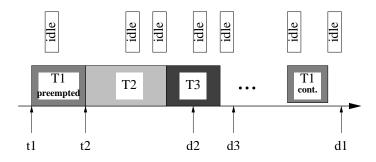

Figure 4.3: Future Slot Reservation

• Backward sweep: Future slots of T1 are allocated from  $T_1$ 's absolute deadline d1 backwards. Any of the idle slots in the maximal schedule become unavailable for other tasks, *i.e.*, these slots are excluded in Equation 4.6.

An example is depicted in Figure 4.3. The upper time line of idle slots presents an excerpt of the maximal schedule that depicts idle task allocations. The lower time line shows the dynamic schedule. Upon release of T2 at time t2, T1 is preempted. Let us assume that T1 does not have sufficient static slots (three slots) beyond t2 to finish its execution. It has to rely on future idle slots. During T2's execution, T3 is released. Both T2 and T3 have earlier deadlines than T1 (d2 < d3 < d1). Subsequently, T1 only resumes after T3 completes.

Future slot allocation of T1 depends on the chosen scheme. The forward sweep results in zero idle slack for T2 and T3 since idle slots during the tasks' periods are not sufficient to cover T1's future execution budget. The backward sweep, on the other hand, reserves the last 3 idle slots from d1 backwards. T2 and T3 have two and one idle slots left, which makes frequency scaling still possible.

Overall, the forward sweep is not as greedy as the backward sweep in the sense that tasks released prior to the preemption point may not be scaled due to T1's future slots. A forward sweep is likely to result in zero slack for the preempting task T2, if  $P2 \ll P1$ , *i.e.*, the period of  $T_2$  is much shorter than  $T_1$ 's period. Fewer idle slots are available in the forward sweep scheme, which may not suffice to cover T1's future requirements. The backward sweep always results in a more greedy solution in delaying the requirements of T1 as late as possible. This is consistent with the observation that early completion is likely to generate slack for every task, a property inherent to our algorithm.

# Chapter 5

## **Feedback Controller**

This chapter first reviews the basic PID feedback control design. It then presents a single proportional-feedback control design, a multi-input control design, and a single-input control design for our DVS algorithm. Finally, the stability of the feedback-DVS system is analyzed.

#### 5.1 Basic PID Control

Equation 4.3 shows that the scaling factor  $\alpha$  of a task  $T_i$  depends not only on the amount of available slack but also on  $C_i^A$ , the number of execution cycles assigned to the first subtask  $T_A$ . Static slack utilization and dynamic slack passing, as described in the previous chapters, help us determine the amount of slack available for each task. In this section, we focus on another key issue, *i.e.*, how to determine the value of  $C_i^A$ . Since  $C_i^A$  is based on the estimated worst-case execution time of the first subtask  $T_A$ , our objective is to let  $C_i^A$  approximate  $T_{ij}$ 's actual execution time  $c_{ij}$  so that  $T_{ij}$  can complete before it enters the second subtask  $T_B$ . Most of all, when  $T_{ij}$ 's actual execution time  $c_{ij}$  does not exceed  $C_i^A$ , all of  $T_{ij}$  executes at a low frequency corresponding to  $\alpha$ . It is not necessary for  $T_{ij}$  to switch to the maximum processor frequency. Hence, a near-optimal energy consumption is obtained.

In real-time applications, the actual execution time  $c_{ij}$  of each task  $T_i$  often experiences fluctuations over different jobs. The fluctuations may result in tendencies

leading to higher processing demands up to some peak point and receding demands after that point. Past work in dynamic real-time scheduling has demonstrated that adaptive techniques derived from control theory can enhance a schedule by reacting to tendencies in execution time fluctuations [41]. In order to devise a DVS algorithm adaptive to such a dynamic environment, we integrate a closed-loop feedback controller into our DVS systems.

Feedback control is one of the fundamental mechanisms for dynamic systems to achieve equilibrium. In a feedback system, some variables, *i.e.*, controlled variables, are monitored and measured by the feedback controller and compared to their desired values, so-called set points. The differences (errors) between the controlled variable and the set point are fed back to the controller repeatedly. Corresponding system states are usually adjusted according to the differences to let the system variables approximate the set points as closely as possible.

PID-feedback control is a continuous feedback controller capable of providing sophisticated control response. The controlled variable can usually reach its set point and stabilize within a short period. A PID controller consists of three different elements, namely, proportional control, integral control, and derivative control. Proportional control influences the speed of the system adapting to errors, which is defined as the difference between the controlled variable and the set point, by a pure proportional gain item. Integral control is used to adjust the accuracy of the system through the introduction of an integrator on past error histories. Derivative control usually increases the stability of the system through the introduction of a derivative of the errors.

The PID feedback controller can be described in three major forms: the ideal form, the discrete form and the parallel form. Although the discrete form is often used in digital algorithms to keep tuning similar to electronic controllers, the parallel form is the simplest one. The integral and derivative actions are independent of the proportional gain in the parallel form. We choose the following parallel form as the basis of our PID feedback implementation:

$$output = K_P \times \epsilon_i + \frac{1}{K_I} \int \epsilon_i \, dt + K_D \frac{d\epsilon_i}{dt} \tag{5.1}$$

where  $K_P$ ,  $K_I$  and  $K_D$  are the proportional, integral and derivative parameters, respectively, and  $\epsilon(t)$  is the system error. The transfer function of the PID controller in the Laplace-domain (s-domain) is given by:

$$G_P(s) = K_P + \frac{K_I}{s} + sK_D \tag{5.2}$$

### 5.2 Proportional Feedback Control Design

A periodic real-time workload may exhibit a relatively stable behavior during a certain interval of time. Thus, the actual execution time of different jobs remains nearly constant or only varies within a very small range. For such workloads, we use a specific PID feedback controller, which includes only a proportional control element. We choose the value of  $C_i^A$  as the controlled variable while  $c_{ij}$  is chosen as the set point.  $C_i^A$  is chosen as 50% of the WCET for the first job of each task. While half of the task's execution is budgeted at a low frequency, half of it is reserved at the maximum frequency. The task can still meet its deadline, even if the worst case is exhibited. Initially, the energy consumption may be significant and is likely to differ from the optimal case due to inappropriate estimations of the actual execution time. Over time, we replace  $C_i^A$  with the actual execution time of the task based on the execution time fed back after each task completion. The average value of execution times over past executions is utilized to anticipate future  $C_i^A$  portions. On the average, this scheme allows us to complete the entire task's budget at a low frequency level, which closely approximates the optimal energy-saving schedule. Let  $C_{ij}^A$  be the anticipated worst case execution time of the first sub-task of job  $T_{ij}$ . We define the following equations to get  $C_{i,j+1}^A$ , the anticipated worst case execution time of the first sub-task of job  $T_{i,j+1}$ :

$$C_{i1}^{A} = 0.5 \times WCET$$

$$C_{i,j+1}^{A} = (C_{ij}^{A} \times (j-1) + c_{ij})/j, \quad j \ge 1$$

(5.3)

where  $c_{ij}$  is the actual execution time of the  $j^{th}$  job of task  $T_i$ . Each time a job completes execution, its actual execution time is fed back and aggregated to anticipate the next job's actual execution time, which is further used to calculate an ideal scaling factor for that task.

Although such a proportional feedback scheme only considers a pure gain adjustment over the anticipated  $C_i^A$  value, it works well for real-time task sets where each task either has a constant actual execution time or it has an execution time varying within a small bounded range. For task sets with highly fluctuating execution times, more sophisticated feedback schemes are required, which is detailed in the next sections.

### 5.3 Multi-input Control Design

The proportional feedback control described in the previous section follows a proportional adjustment relative to average execution times. In practice, real-time embedded systems, such as audio and video playback or image processing systems, often experience fluctuating execution times of tasks over a period of time. The fluctuations may result in tendencies leading to higher processing demands up to some point and receding demands after this peak point. In order to devise a DVS algorithm adaptive to such a dynamic environment, more sophisticated feedback schemes are needed. According to the objective described above, we design a feedback scheme presented as a multiple-input (MI) control system. For every task  $T_i$  in the system, its  $C_i^A$  value is chosen as the controlled variable while its actual execution time  $c_{ij}$ is chosen as the set point. The system error is defined as the difference between the controlled variable and the set point, *i.e.*,

$$\epsilon_{ij} = c_{ij} - C^A_{ij}.\tag{5.4}$$

The error is measured periodically by the controller. Its output is fed back to the feedback-DVS scheduler to adjust the value for  $C_i^A$ . For *n* tasks in the task set, there are altogether *n* feedback inputs ( $\epsilon_{ij}$ , i=1...n) and *n* system outputs ( $C_i^A$ , i=1...n).

For each task  $T_i$ , let  $C_{ij}^A$  be the estimated  $C_i^A$  value for its  $j^{th}$  job. The following discrete PID control formula is used in our feedback-DVS scheduler:

$$\Delta C_{ij}^A = K_P \times \epsilon_{ij} + \frac{1}{K_I} \sum_{IW} \epsilon_{ij} + K_D \frac{\epsilon_{ij} - \epsilon_i (t - DW)}{DW}$$

$$C_{i,j+1}^A = C_{ij}^A + \Delta C_{ij}^A$$

(5.5)

where  $K_P$ ,  $K_I$  and  $K_D$  are proportional, integral, and derivative parameters, respectively.  $\epsilon_{ij}$  is the monitored error. The output  $\Delta C_{ij}^A$  is fed back to the scheduler and is used to regulate the next anticipated value for  $C_i^A$ . IW and DW are tunable window sizes such that only the errors from the last IW (DW) task jobs will be considered in the integral (derivative) term. We use DW = 1 to limit the history, which ensures that multiple feedback corrections do not affect one another. The three control parameters  $K_P$ ,  $K_I$  and  $K_D$  adjust the control response amplitude and its dynamic behavior with great versatility. It is therefore important to choose and tune these parameters for the controller. The process of adjusting the control parameters is compromised among different system performance metrics. For example, the system may be tuned to have either a stable but slow control response, or an instable but dynamic control response. What is preferred in our system is a sufficiently rapid and stable control output during the entire scheduling process.

This multi-input model achieved significant energy savings as shown in Chapter 7, but it also exhibited some drawbacks when we implemented it on real embedded platforms. The multi-input control structure increases the total memory requirements of the system, since the DVS scheduler needs to create an individual feedback controller for every task in the task set. Each feedback controller maintains a queue structure in order to store the execution time history of previous jobs, which requires additional memory space proportional to the length of the queue as well as the total number of tasks. Such per-task memory requirements limit the maximal number of tasks an embedded system can sustain. Furthermore, the multi-input model manipulates multiple inputs and multiple outputs simultaneously, which increases the complexity of the scheduler design and implementation. Given the difficulty of precisely characterizing the behavior of a control system, it also adds complexity to the theoretical analysis of the system. In order to address the drawbacks brought by the complexity of the MI control system, we transform the above MI model into a single-input (SI) control model in the following.

### 5.4 Single-input Control Design

We now present a simplified design for the system model.

Instead of using  $C_i^A(i = 1...n)$  as the controlled variable for each task  $T_i$  and creating *n* different feedback controllers for *n* different tasks, we now define a single variable r as the controlled variable for the entire system as:

$$r_j = \frac{1}{n} \sum_{i=1}^n \frac{C_{ij}^A - c_{ij}}{c_{ij}}$$

(5.6)

where j is the index of the latest job of task  $T_i$  before the sampling point.  $r_j$  describes the average difference between tasks' actual execution times and their corresponding  $C_i^A$  values. Our objective is to make r approximate 0 (*i.e.*, the set point). The system error becomes

$$\epsilon(r_j) = r_j - 0. \tag{5.7}$$

where  $\epsilon(r_j)$  reflects the error of the entire task set and is not a function of a particular task  $T_i$  anymore.  $\epsilon(r_j)$  is further fed back to the PID scheduler to regulate the controlled variable r. The PID feedback controller is now defined as:

$$\Delta r_j = K_P \times \epsilon(r_j) + \frac{1}{K_I} \sum_{IW} \epsilon(r_j) + K_D \frac{\epsilon(r_j) - \epsilon(r_{j-DW})}{DW}$$

$$r_{j+1} = r_j + \Delta r_j$$

(5.8)

where  $K_P, K_I$  and  $K_D$  are the PID parameters. IW and DW are the integral and derivative window sizes.

When job  $T_{ij}$  completes, we adjust the  $C_A$  value for  $T_{i(j+1)}$  by  $C_{i,j+1}^A = r_j \times c_{ij} + c_{ij}$ , which is used by the DVS scheduler to calculate the scaling factor  $\alpha$  and to determine a processor frequency and voltage for the next job. Such a single controller mechanism is easy to implement because one feedback controller suffices for the entire system, which reduces the complexity and overhead of the feedback DVS algorithm. It reduces the memory requirement of the system since only one global feedback queue needs to be created instead of n different queues for n different tasks in the multi-input feedback scheme. Such a transformation simplifies the control system so that there is only one system input  $\epsilon(t)$  and one system output r. It eases the analysis and implementation of the feedback controller in our scheduler. But a drawback of the model is that it does not provide direct feedback of the  $C_i^A$  value for each individual task. A zero value of r may not necessarily imply that each task  $T_i$ 's  $C_i^A$  has approximated its actual execution time. It is only an imprecise description of the original scheduling objective and may take longer to get the system into a stable status. But we expect that this model still captures the characteristics of the overall system behavior and leads to acceptable performance, which has been confirmed in our experiments. In the following, we analyze the system to assess the stability of our control model.

## 5.5 Stability Analysis of the Single-input Feedback Control

Stability is an important metric for real-time control systems. A control system is stable if its controlled variables are always bounded for bounded input performance references and disturbances. In order to analyze the stability of the above single-input control model, we compute its transfer function in the Laplace domain. The transfer function of the PID controller is defined as:

$$G_{PID}(s) = K_P + \frac{K_I}{s} + K_D s \tag{5.9}$$

The transfer function between  $r_j$  and  $C_i^A$  can be derived by taking derivative of both sides of the equation 5.6:

$$G_r(s) = Ms \tag{5.10}$$

where  $M = \frac{1}{n} \sum_{i=1}^{n} \frac{1}{c_i}$ . Therefore, the transfer function of the entire closed-loop feedback system can be computed as:

$$\frac{G_{PID}(s)G_r(s)}{1 + G_{PID}(s)G_r(s)} = \frac{MK_P s + MK_I + MK_D s^2}{1 + MK_P s + MK_I + MK_D s^2}$$

(5.11)

According to control theory, a system is stable if and only if all the poles (the denominator of its transfer function) are in the negative half-plane of the s-domain. From Equation 5.11, we infer the poles of our system as

$$\frac{-MK_P \pm \sqrt{MK_P^2 - 4MK_D(MK_I + 1)}}{2MK_D}$$

(5.12)

Note that  $-MK_P + \sqrt{MK_P^2 - 4MK_D(MK_I + 1)}$  is always less than 0 when  $MK_P^2 - 4MK_D(MK_I + 1) > 0$ . Hence, all the poles are in the negative half-plane of the s-domain. Therefore, the stability of the above system is ensured.

## Chapter 6

## Algorithm and Its Correctness

This chapter presents an algorithmic description of the feedback-DVS scheme in pseudo-code. Some examples are then given to explain the scenario when the algorithm is applied on real-time task sets.

### 6.1 Algorithm Description

An algorithmic description of our feedback-DVS scheme with the PID feedback control is given in Algorithm 1. The following notations are used in the algorithm description:

- $T_{ij}$ : the j-th job of task  $T_i$

- prev: the index of the previous job immediately scheduled before  $T_{ij}$

- *now*: the current time

- $P_i$ : the Period of  $T_i$

- $d_{ij}$ : the absolute deadline of  $T_{ij}$

- $C_i$ : the WCET of  $T_i$  (without scaling)

- $C_i^A$ : the anticipated worst-case execution time of the first sub-task (low frequency portion) of  $T_i$

- $C_i^B$ : the anticipated worst-case execution time of the second sub-task (high frequency portion) of  $T_i$

- $c_{ij}$ : the actual execution time of  $T_{ij}$  up to now (with scaling)

- $K_P, K_I, K_D$ : the PID parameters

- *IW*, *DW*: the integral and derivative window size

- $L_{ij}$ : the worst-case remaining execution time of  $T_{ij}$  (without scaling)

- *slack*: the current slack of the system

- idle(t1..t2): the amount of idle slots between times [t1,t2]

- completed(t1..t2): slots of already completed tasks between times [t1,t2]

- $slots(T_{ij}, t1..t2)$ : the amount of time slots reserved for  $T_{ij}$  in the worst case between times [t1,t2]

- f: the processor frequency

- $f_m$ : the maximal processor frequency

- $\alpha$ : the frequency scaling factor

This algorithm integrates the PID feedback scheme and preemption-handling with future slot reservation. Only the MI control model is presented in the pseudo-code. The SI model is implemented in a similar way. The online complexity of our algorithm is O(n) for n tasks, because the length of slots in the maximal schedule during the interval between the release time and deadline of the current task has to be updated when a task is released or completes. The number of slots in this interval is bounded by the number of tasks because only a constant number of jobs for each task and a constant number of preemptions may occur in this interval.

Next, let us see some examples of applying the algorithm on real-time task sets.

### 6.2 Examples

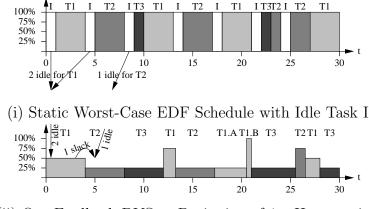

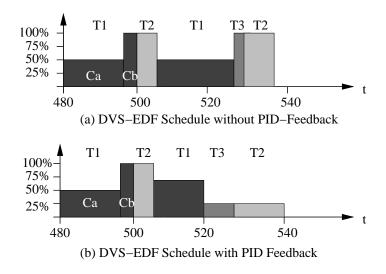

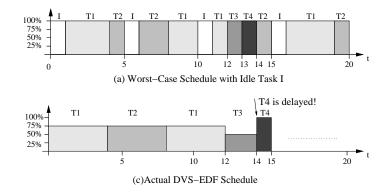

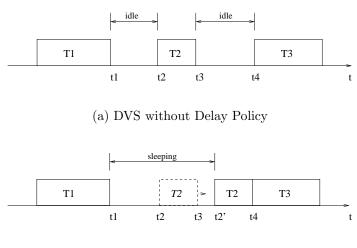

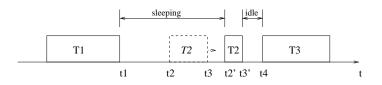

Figure 6.1(i) is an example of a static maximal EDF schedule, constructed offline. The example includes a task set of three tasks T1={3,8}, T2={3,10} and T3={1,14}, where  $T_i = \{C_i, P_i\}$  denotes task  $T_i$ 's worst case execution time  $C_i$  and its period  $P_i$ . An idle task I={1,4} is also included in the maximal schedule to fill underutilized processor time niches. Every task's actual execution time is one except the first job

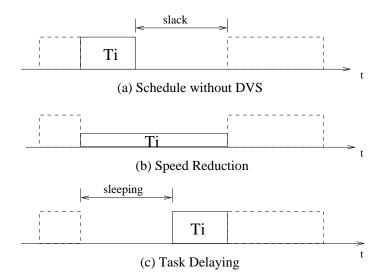

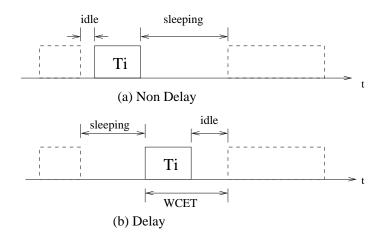

#### Algorithm 1: Feedback-DVS