#### ABSTRACT

SARKAR, ABHIK. Predictable Task Migration Support and Static Task Partitioning for Scalable Multicore Real-Time Systems. (Under the direction of Frank Mueller.)

Multicores are becoming ubiquitous, not only in general-purpose but also embedded computing. This trend is a reflection of contemporary embedded applications posing steadily increasing demands in processing power. On such platforms, prediction of timing behavior to ensure that deadlines of real-time tasks can be met is becoming increasingly difficult. While real-time global/semi-partitioned multicore scheduling approaches help to assure deadlines based on firm theoretical properties, their reliance on task migration poses a significant challenge to timing predictability in practice. Task migration actually (a) reduces timing predictability for contemporary multicores due to cache warm-up overheads, (b) renders locking of cache lines infeasible for multicore real-time systems and (c) increases traffic on the network-on-chip (NoC) interconnect. Additionally, prior work in static task partitioning on multicore architectures focuses on shared cache organization with a fixed number of cores. Such schemes are not suitable for static partitioning on scalable multicore architectures that feature private cache organization. We attempt to address these limitations in this dissertation.

The following are the key contributions of this work:

- 1. First, a task migration into two cores imposes cache warm-up overheads on the migration target, which can lead to missed deadlines for tight real-time schedules. We propose a novel push-assisted cache migration model to pro-actively migrate cache lines through novel software and micro-architectural support. Our mechanism imposes cache migration delays at a fraction of the task's execution time. This delay can be steered to fill idle slots in the schedule, *i.e.*, it does not contribute to the execution time of the migrated task. We also propose micro-architectural modifications that further reduce the delay and bus traffic.

- 2. Second, locked cache lines that are predominantly used in real-time systems are immobile during task migration. We address this issue by extending the push-assisted migration model with several cache migration techniques to efficiently retain locked cache lines on a bus-based chip multi-processor architecture. We also provide deterministic migration delay bounds that help schedulers to decide which migration technique(s) to utilize while migrating a single or multiple tasks. This information also allows the scheduler to determine feasibility of task migrations, which is critical for the safety of any hard real-time system. Such proactive migration of locked cache lines in multicores is unprecedented to our knowledge.

3. Third, we further the use of locked caches on scalable multicore architectures by analyzing its impact on static task partitioning algorithms. In shared cache architectures, a single resource is shared among all the tasks. However, in scalable cache architectures with private caches, conflicts exist only among the tasks scheduled on one core. This calls for a cache-aware allocation of tasks onto cores. Here, we propose a novel variant of the cache-unaware First Fit Decreasing (FFD) algorithm called the Naive locked First Fit Decreasing (NFFD) policy. We propose two cache-aware static scheduling schemes: (1) Greedy First Fit Decreasing (GFFD) and (2) Colored First Fit Decreasing (CoFFD) for task sets where tasks do not have intra-task conflicts among locked regions (Scenario A). NFFD is capable of scheduling high utilization task sets that FFD cannot schedule. CoFFD consistently outperforms GFFD requiring a lower number of cores and lower system utilization. For a more generic case where tasks have intra-task conflicts, we split the task partitioning into two phases: Task Selection and Task Allocation (Scenario B). Instead of resolving conflicts at a global level, these algorithms resolve conflicts among regions while allocating a task onto a core and perform unlocking at region-level instead of task-level. We show that a combination of our novel Dynamic Ordering (Task Selection) with Chaitin's Coloring (Task Allocation) scheme reduces the number of cores required considerably over a basic scheme (combination of Monotone Ordering and Regional FFD).

Overall, this dissertation suggests that deployment of locked caches and hardware support for cache migration on scalable multi-processors can enable more predictable and efficient multiprocessor scheduling. © Copyright 2012 by Abhik Sarkar

All Rights Reserved

# Predictable Task Migration Support and Static Task Partitioning for Scalable Multicore Real-Time Systems

#### by Abhik Sarkar

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

Computer Science

Raleigh, North Carolina 2012

#### APPROVED BY:

| James Anderson |                           | Xuxian Jiang |

|----------------|---------------------------|--------------|

|                |                           |              |

|                |                           |              |

|                |                           |              |

| Helen Gu       |                           | James Tuck   |

|                |                           |              |

|                |                           |              |

|                |                           |              |

|                | Frank Mueller             |              |

| Ch             | air of Advisory Committee |              |

## **DEDICATION**

To Ma and Baba.

#### **BIOGRAPHY**

Abhik Sarkar was born and raised in New Delhi, India. He attended St. Xavier's high school, Delhi. Thereafter, to pursue a degree in Electronics and Communication Engineering he attended Delhi University. After completing his undergraduate degree, he worked for two years as an Associate Systems Lab Engineer in Advanced Systems Technologies group at STMicroelectronics, India. While working in a research group led by Dr. Kaushik Saha, he developed a keen interest in parallel processing and parallel computer architectures. During his tenure at ST, he worked on parallel implementations of audio/video codecs.

In fall 2005, he moved to North Carolina as a graduate student in the Department of Electrical and Computer Engineering at North Carolina State University (NCSU). There, he worked under the guidance of Dr. Yan Solihin and Dr. Joe Defenderfer (Tekelec Corp.). As a part of his Master's degree in Computer Engineering, he developed libraries to assist development of lock-free data structures. Thereafter, he joined the Department of Computer Science at NCSU in 2008 to continue his graduate studies as a doctoral student in systems research group led by Dr. Frank Mueller. Since then he has been pursuing his research interests in hardware/software co-design for predictable multicore real-time systems. During his doctoral studies he also interned in research labs at Intel and VMware. After finishing his doctoral studies at NCSU, he will be joining Intel Corporation.

#### ACKNOWLEDGEMENTS

It had drama, excitement, periods of boredom, moments of brilliance, dozes of good calls and poor judgments, tests of patience, lack of concentration, desperate dives, constant pressure, words of confidence, disappointing runs, lots of prayers, back and wrist problems, distance from family, but at the end a tryst with tearful celebrations. As every cricket enthusiast would call it the description of a single test inning played by the god of cricket, Sachin Ramesh Tendulkar. For me, that is the description of my PhD. For non-cricket playing souls, please enlighten yourself with a copy of May'12 edition of TIME magazine. During this period, one of the lessons I have learnt is to be grateful, which makes the acknowledgments an integral part of this dissertation.

Firstly, I would like to thank my parents for teaching me the importance of perseverance, for inspiring me with their selflessness, and for all the heart-felt wishes that have made it possible. In their lives, my father wanted to have an engineering degree and my mother wanted to be a doctor. This dissertation strikes two birds with one stone. How? This is left as an exercise for the reader. Ma/Baba, I dedicate this dissertation to you.

Secondly, I would like to thank my advisor Dr. Frank Mueller. His commitment towards me and my research has always motivated me to do better. Throughout my research, he has given me invaluable advice and guidance, both in research and life. His constant flow of ideas has amazed me but at the same time, challenged me to think beyond the conventional. His method of operating with doodles on discussion boards has enabled me to appreciate the concept of controlled chaos. It has been an invaluable experience to work with him and it is impossible for me to express my gratitude towards him in words.

I am grateful to Paula D'Onofrio for being the motherly figure to me when I needed the most. Her unconditional support for my dreams and aspirations is the integral part of maintaining my focus in this long drawn process. Her furry feline kids Bella, Willoughby, and Oliver have been great stress busters. Their research on the importance of slumber as a mechanism to relieve stress has motivated me to follow suit. I am grateful to Dr. Robert Jenks whose words of encouragement have imbibed self belief. He made me realize that wooden block puzzles can have a humbling effect. I thank Corrine Shuster for making me realize the importance of gratitude and savoring life in every situation.

Special thanks to Dr. James Tuck for helping me with simulation environments and the discussions that have helped me understand computer architecture at depth. I sincerely thank Dr. James Anderson, Dr. Helen Gu and Dr. Xuxian Jiang for their advice, suggestions and questions that have contributed substantially to making this thesis comprehensible.

I would like to thank Nikhil Deshpande, with whom I have shared a large part of my graduate

student life. We started by being disgruntled room mates but over the period of seven years, I have developed immense respect for this class act. Then there were two, Suresh Thummalapenta and Gaurav Bawa, who are the embodiment of hard work and Indian community networking. Special thanks to John Whitlow for accommodating me under his roof that I have been calling home during my final year of PhD. You can only wish to have a landlord who ships Garra Rufa fish to get you manicured and pedicured while you write your dissertation. I would like to thank this small family of spiritual beings at Ganesh Place in Durham, who have made me smile through the tough times either with profound love or with gifted goofiness. I am grateful to Dorothy for including me in her annual "feastivities" with the "Mazzitellis", a musical family with a big heart. Thanks Joe for making this world a little more musical. Ferrrnando Rubio, I thank you for painting my graduate student life with shades of fun loving salsa attitude.

And then comes the turn of the Beagle Boys at the Systems Research Lab in NC State. Christopher Zimmer is the "Ma Beagle", who runs the show and keeps an eye on the door whenever anyone walks in. David Fiala is the "Bigtime Beagle", who leads the pack to everything mischievous. Arash Rezaei is the "Bebop Beagle" wearing jazzy outfits. Dr. James Elliotte is the personification of "Babyface Beagle" for the obvious reasons. Yangpeng Zhang and Xing Wu represent the "Bankjob Beagle" with exceptional soccer and publishing skills. And I am the "Burger Beagle" for obvious reasons again. As a Beagle Boy I have loved the passionate discussions on research and everything besides that. Without them I would not have learnt the importance of laying low and keeping the banter-guns loaded. Thanks to all of you for being a part of my clique.

Over the years many graduate students have left a brush stroke or two on the canvas of my life. Amit Awekar, Ravi Ramaseshan, Prasad Wagle, Sandeep Navada, Niket Chaudhary, Devesh Tiwari, Xiaowei Jiang, Siddharth Chhabra, Brian Rogers, Nicky Mahilani, Bala Subramanya Bhat, Karthik Babu, and many more. I thankful to all of you for being a part of my journey.

Since this all started when I was a student at Delhi University and an employee at STMicroeletronics in India, I would like to thank Dhananjay Gadre, Dr. Raj Senani, Saibal Dutt, Dr. Mona Mathur, Dr. Kaushik Saha, Srijib Narayan Maiti, Surinder Pal Singh, Yogesh Kumar Soni, Sumit Johar and Sandeep Dabas for motivating me with their brilliance. Special thanks to Rahul Gandhi for being there when I needed him the most.

Last but not the least, I would like to thank the staff of Office of International Students, Department of Computer Science, and Graduate School Office, at NC State and to everyone else behind the scenes for all their help. Special thanks to Dr. Douglas Reeves and Dr. David Thuente for helping me through the process of graduate studies at NC State.

To all of you who have been mentioned, I wish you the very best in life and I hope to keep running into you. To those whom I have inadvertently omitted, I sincerely apologize and

request you to let me know how I can make up for it.

## TABLE OF CONTENTS

| List of | Tables                                                               | ix             |

|---------|----------------------------------------------------------------------|----------------|

| List of | Figures                                                              | X              |

| Chapte  | er 1 Introduction                                                    | 1              |

| 1.1     | Real-Time Systems                                                    | 1              |

| 1.2     | Multicore Architectures                                              | 9              |

| 1.3     | Multicore Real-time Systems                                          | 14             |

|         | · · · · · · · · · · · · · · · · · · ·                                | 14             |

|         |                                                                      | 15             |

| 1.4     |                                                                      | 16             |

| 1.5     |                                                                      | 17             |

| 1.6     | 0.1                                                                  | 18             |

| Chapte  | er 2 Push-Assisted Migration of Real-Time Tasks in Multicore Proces- |                |

| Chapte  |                                                                      | 19             |

| 2.1     |                                                                      | 19             |

| 2.2     | Introduction                                                         | 20             |

| 2.3     |                                                                      | $\frac{1}{21}$ |

| 2.4     | ·                                                                    | 26             |

| 2.5     | 1                                                                    | 28             |

|         | 2.5.1 The Conventional Pull Model                                    | 28             |

|         | 2.5.2 The Pre-fetch Task Model(PTM)                                  | 28             |

|         | 2.5.3 The Push-assisted Cache Migration Model                        | 30             |

| 2.6     | g .                                                                  | 33             |

| 2.7     | Evaluation                                                           | 34             |

| -       |                                                                      | 34             |

|         |                                                                      | 36             |

| 2.8     | 9                                                                    | 41             |

| 2.9     |                                                                      | 42             |

| CI.     |                                                                      |                |

| Cnapte  | er 3 Deterministic Task Migration for Hard Real-Time Tasks in Mul-   | 1 1            |

| 9.1     | ticore Processors                                                    |                |

| 3.1     | Introduction                                                         |                |

| 3.2     | v                                                                    | 46             |

| 3.3     | 1                                                                    | 49             |

| 3.4     | Migration Models                                                     | 52             |

|         |                                                                      | 52             |

|         | 3.4.2 Regional Cache Migration (RCM)                                 | 52             |

|         | 9                                                                    | 55             |

|         | 9 ( )                                                                | 62             |

| 3.5     | Simulation Platform                                                  | 65             |

| 3.6    | Evaluation                                                                         | 66         |  |  |

|--------|------------------------------------------------------------------------------------|------------|--|--|

|        | 3.6.1 RCM v/s. SSCM                                                                |            |  |  |

|        | 3.6.2 Pipelined RCM techniques                                                     |            |  |  |

|        |                                                                                    | 67         |  |  |

|        | 3.6.4 Parallel vs. Pipelined Cache Migration                                       | 39         |  |  |

| Chanta | on 4 Static Teel, Doutitioning for Locked Cookes in MultiCone Deel                 |            |  |  |

| Chapte | er 4 Static Task Partitioning for Locked Caches in MultiCore Real-<br>Time Systems | , 1        |  |  |

| 11     | · ·                                                                                | <b>'</b> 1 |  |  |

| 4.1    |                                                                                    | 71<br>76   |  |  |

| 4.2    |                                                                                    | 76<br>76   |  |  |

| 4.3    |                                                                                    | 76         |  |  |

| 4.4    | 0                                                                                  | 78         |  |  |

|        |                                                                                    | 78         |  |  |

|        | 9                                                                                  | 30         |  |  |

| 4.5    | 0                                                                                  | 38         |  |  |

|        |                                                                                    | 88         |  |  |

|        |                                                                                    | 39         |  |  |

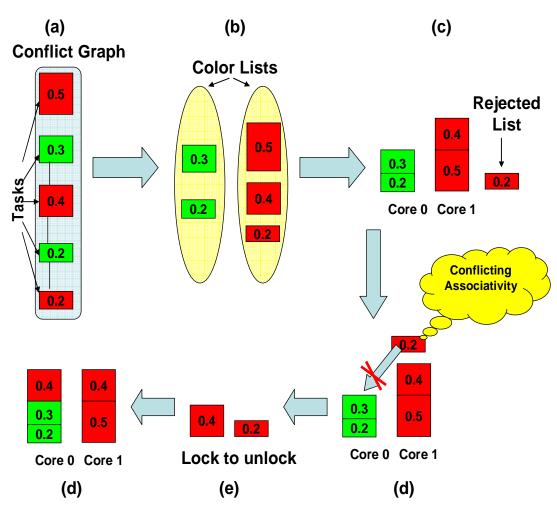

| 4.6    | S                                                                                  | 92         |  |  |

| 4.7    |                                                                                    | 93         |  |  |

| 4.8    |                                                                                    | 95         |  |  |

|        |                                                                                    | 96         |  |  |

|        | 4.8.2 Scenario B                                                                   | 98         |  |  |

| Chapte | er 5 Conclusion and Future Work                                                    | <b>)</b> 2 |  |  |

| 5.1    | Conclusions                                                                        |            |  |  |

| 5.2    | Future Work                                                                        |            |  |  |

|        | 5.2.1 Holistic Task Partitioning on Scalable Multicore Real-Time Systems 10        |            |  |  |

|        | 5.2.2 Thermal Analysis of Multicore Real-Time Systems                              |            |  |  |

|        |                                                                                    |            |  |  |

| Refere | ${ m nces}$                                                                        | )9         |  |  |

## LIST OF TABLES

| Table 2.1  | WCET Benchmarks                                                                  | 22  |

|------------|----------------------------------------------------------------------------------|-----|

| Table 2.2  | Task migration & dilation in WCET                                                | 23  |

| Table 2.3  | Matrix multiplication WCET v/s matrix size                                       | 23  |

| Table 2.4  | Bubble Sort WCET v/s Number of Elements                                          | 24  |

| Table 2.5  | Simulation Parameters                                                            | 33  |

| Table 2.6  | Prefetch Task Model & Potential to Bound WCET                                    | 35  |

| Table 2.7  | WCM Performance & Overhead                                                       | 36  |

| Table 2.8  | Migration Paradigms and Percent Additional Execution over WCET $$                | 38  |

| Table 2.9  | Cache Migration Overhead cycles over WCET [percent]                              | 38  |

| Table 2.10 | Cache Migration and Bandwidth Overhead<br>[number of requests] $\ . \ . \ . \ .$ | 40  |

| Table 3.1  | Experimental Benchmarks                                                          | 47  |

| Table 3.2  | Impact of Cache Locking (when contented with cnt)                                | 48  |

| Table 3.3  | Simulation Parameters                                                            | 66  |

| Table 3.4  | Migration Delays: RCM vs SSCM                                                    | 67  |

| Table 3.5  | Pipelined Cache Migration                                                        | 68  |

| Table 3.6  | SSCM Variants                                                                    | 68  |

| Table 3.7  | Parallel vs Pipeline                                                             | 70  |

| Table 4.1  | Locking and Conflict Analysis for 32 Tasks                                       | 74  |

| Table 4.2  | System Parameters                                                                | 95  |

| Table 4.3  | Allocated Cores for Cache-aware & Cache-unaware Schemes                          | 96  |

| Table 4.4  | Allocated Cores for CoFFD & GFFD: All Tasks Locked                               | 97  |

| Table 4.5  | CoFFD vs GFFD: Selected Tasks Unlocked                                           | 97  |

| Table 4.6  | Mono+RFFD vs. Mono+CC for High Conflict: Number of cores allocated               | 99  |

| Table 4.7  | Mono+RFFD vs. Mono+CC for low Conflict: Number of cores allocated .              | 99  |

| Table 4.8  | Average allocations performed by Scenario B algorithms: Number of cores          |     |

|            | allocated                                                                        | 100 |

| Table 4.9  | Best and Average improvement by Dyn+CC over Mono+RFFD                            | 100 |

| Table 4.10 | CoFFD vs Dyn+CC: task vs region unlocking                                        | 101 |

| Table 5.1  | Average core allocation: Sensitivity to Memory Latency                           | 107 |

## LIST OF FIGURES

| Figure 1.1  | Generic view of Cache Architecture                          | . 5   |

|-------------|-------------------------------------------------------------|-------|

| Figure 1.2  | MESI-Locally Initiated Accesses                             | . 11  |

| Figure 1.3  | MESI-Remotely Initiated Accesses                            | . 12  |

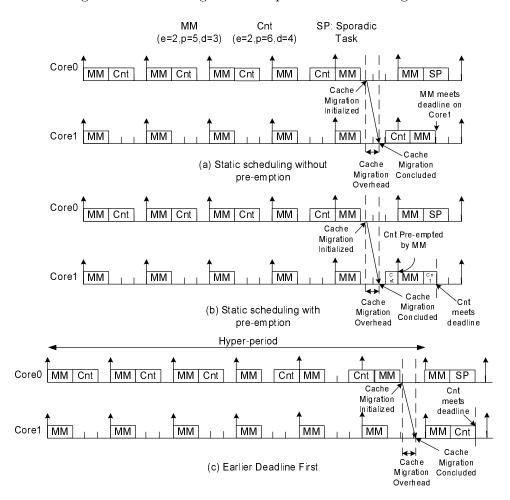

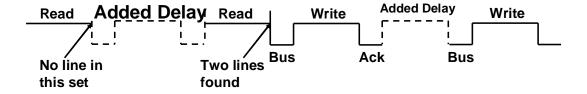

| Figure 2.1  | Task Execution amid Task Migration                          |       |

| Figure 2.2  | Task migration and scheduling anomalies                     | . 25  |

| Figure 2.3  | Task Migration Coupled with Cache Migration                 | . 27  |

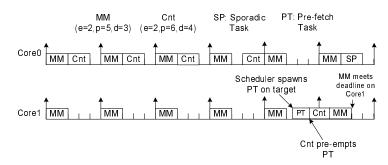

| Figure 2.4  | Task Migration with Pre-fetch Task support                  | . 29  |

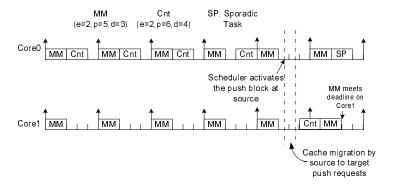

| Figure 2.5  | Task Migration with Push-assisted Cache Migration support   | . 30  |

| Figure 3.1  | Symmetric Multi-processors                                  | . 49  |

| Figure 3.2  | Scheduler Initiated Cache Migration Overlaps Slack Time     | . 50  |

| Figure 3.3  | Cache Migration follows Pfair scheduling                    | . 51  |

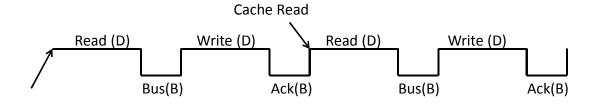

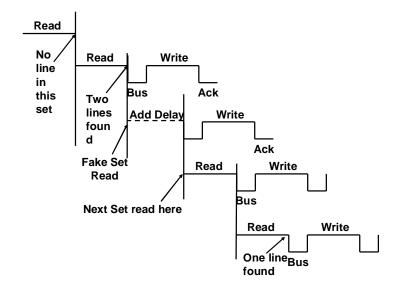

| Figure 3.4  | Regional Cache Migration Operational Sequence               | . 53  |

| Figure 3.5  | Controlled Cache Migration Pipe-lining Operational Sequence | . 54  |

| Figure 3.6  | Streamed Cache Migration Pipe-lining Operational Sequence   | . 55  |

| Figure 3.7  | Parallel Multiple RCMs                                      | . 56  |

| Figure 3.8  | Partial Ordering of Core Pairs                              | . 60  |

| Figure 3.9  | Set-Scan Cache Migration Operational Sequence               | . 62  |

| Figure 3.10 | Conflicts between RCM and SSCM Push Requests                | . 63  |

| Figure 3.11 | Slotted-SSCM Operational Sequence                           |       |

| Figure 3.12 | Slotted-SSCM Pipe-lining Operational Sequence               |       |

| Figure 3.13 | Offline Computation of Migration Delays for Slotted-SSCM    | . 69  |

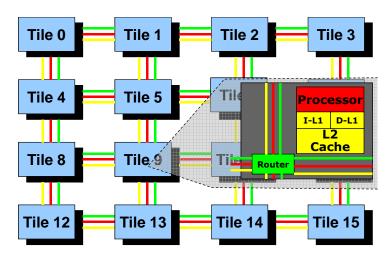

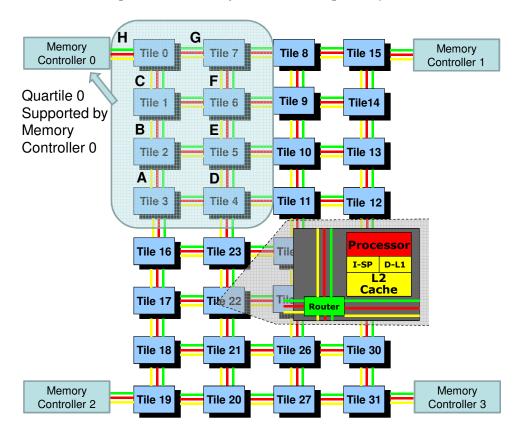

| Figure 4.1  | Tile-based Architecture                                     | . 72  |

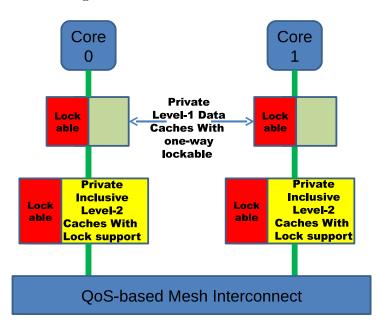

| Figure 4.2  | A Lock-based Architecture                                   | . 77  |

| Figure 4.3  | Greedy First Fit Decreasing in Operation                    | . 81  |

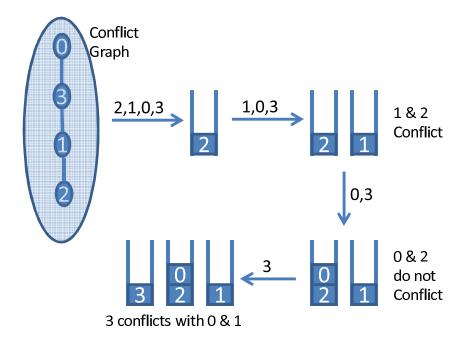

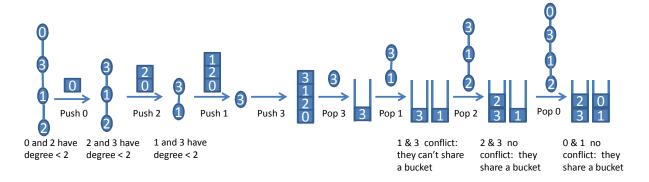

| Figure 4.4  | Chaitin's Coloring in Operation with 2 Colors               | . 83  |

| Figure 4.5  | Task Coloring in Operation                                  | . 86  |

| Figure 5.1  | Memory Traffic Routing of a Quartile                        | . 106 |

## Chapter 1

## Introduction

## 1.1 Real-Time Systems

Real-time Systems are computing environments where temporal correctness is as important as functional correctness. A real-time system is temporally correct if all real-time tasks meet their timing constraints. Control systems use real-time software to operate in a temporally correct fashion in automobiles, aerial vehicles, audio-video devices, medical radiation devices, etc. A single real-time system can be composed of periodically executing real-time tasks that collect information from their environment and trigger a response. A delayed response could result in artifacts that can impact the quality of service or even lead to catastrophic consequences depending upon the purpose of the system. In a mobile device supporting audio/video applications, the frame rate leading to a "flicker-free" visual experience governs the amount of time in which a video frame should be decoded. A delayed response will result in dropping video frames, which in turn impacts the visual experience of the customers. However, such failures do not render a system nonfunctional. Such tasks are called soft real-time tasks and have soft deadlines. In contrast, when tasks in Anti-lock Brake System(ABS) fail, it causes the wheels to lock-up, which could lead to catastrophic consequences like loss of life. Such tasks are called hard real-time tasks and have hard deadlines.

In a system, real-time tasks can be executed periodically, aperiodically or sporadically. Periodic tasks have regular arrival times. Aperiodic and sporadic tasks may have irregular arrival times. Aperiodic tasks have soft deadlines while sporadic tasks have hard deadlines. This work assumes tasks to be periodic. Each task i is periodically released after a time interval of  $P_i$ . Every instance of task i is called a job and denoted as  $J_i^n$  where n is the nth instance of task i. Every real-time task is given a relative deadline  $D_i$ . Every real-time job has to respond before a pre-calculated instant of time called its deadline  $d_i^n$ , which is computed by adding the task's relative deadline,  $D_i$ , to the time instant t at which the nth job of task i was

released. If  $J_i^n$  does not finish execution before  $d_i^n$ , then the job is deemed to have missed a deadline. The relative task deadline can be less than, equal to or greater than a task's period. In our work, we assume that  $D_i \leq P_i$ , which means that  $J_i^n$  has to finish prior to the release of  $J_i^{n+1}$ . The consequence of missing a deadline depends on the criticality of a task. As stated earlier, a task that renders an encoded stream of video frames has a soft deadline. A video rendering task failing to meet a deadline leads to a poorer visual experience. However, if a task that releases brakes fails to meet its deadline in an ABS system, it can cause catastrophic consequences. Such critical tasks have hard deadlines. Tasks with hard and soft deadlines are called hard and soft real-time tasks, respectively. A real-time system is composed of at least a soft/hard real-time task while it can run multiple real-time or non-real-time tasks. In order to reduce operational costs and to leverage the computational capacity of modern processors, real-time systems are usually multi-programmed.

Task scheduler(s) running on these systems are responsible for invoking jobs of periodic tasks. For soft real-time systems, task schedulers may also incorporate a responsive action when a deadline miss is detected. A deadline miss can be detected in several ways. For example, a timer-based interrupt can be scheduled by the task scheduler at  $d_i^n$  for the invocation of  $J_i^n$ . The interrupt will initiate a interrupt routine that checks whether  $J_i^n$  has finished its execution. In case a job misses its deadline, the system has to respond to prevent/reduce subsequent jobs from missing their deadlines. These actions may vary depending upon the implementation of the system. For example, the task scheduler may choose to terminate  $J_i^n$  or skip job  $J_i^{n+1}$ . In case certain subsequent jobs are dependent upon  $J_i^n$ , then those jobs need to be skipped as well. In contrast, for hard real-time systems it becomes imperative that each of the task meet their deadlines for it to be functional. For such systems, the developer needs to analyze the tasks and make sure that all the tasks meet their deadline prior to launching the system. This is called schedulability analysis. Schedulability analysis requires the following information:

- 1. The Worst-Case Execution Time (WCET) of each the task represented as  $E_i$ . This can be obtained by

- (a) Static analysis of the source code. This has been a research topic for the real-time systems community for more than three decades. With the advent of multicores, multi-level caches and network-on-chip (NoC), it is still an open research area. A static analysis tool would require certain parameters of a processor architecture, e.g., execution latency of instructions in an Instruction Set Architecture (ISA), access latency at different levels of memory hierarchy, number of cycles lost due to a branch instruction on a system with branch prediction turned off etc. The tool then parses the instructions and, using an intermediate representation (IR), computes the worst case number of cycles needed for each basic block to execute. Parsing the IR, like an

abstract syntax tree, allows it to converge to a worst case execution path (WCEP) that delivers the WCET. Since programs usually execute in control flow of tight loops, the static analysis tool needs the information on the maximum number of iterations of each loop. Several static analysis tools are available though they are prone to deliver high upper bounds. However, if static analysis of a task delivers a WCET lower than the period, the bound is considered safe since the real-time task cannot exceed this bound.

(b) Dynamically observing the execution time of the task with an exhaustive input set. This scheme is widely used as certain parameter values assumed by static analysis tools, like using an upper bound on load-dependent branches, might just be too high than the ones observed in practice.

This allows us to compute the task density as  $\frac{E_i}{D_i}$ . This is the computational demand of a task on a computational resource.  $\frac{E_i}{P_i}$  gives us the task utilization, which is the same as task density when  $P_i = D_i$ .

- 2. A schedulability test that governs whether a task set is schedulable or not on a given computing resource. If a task set passes the schedulability test, then it guarantees that all the tasks will meet their deadlines. However, a schedulability test is dependent upon the scheduling algorithm. Over the past four decades, various task scheduling algorithms have been proposed on a computing resource. They are broadly characterized as

- (a) Clock driven: These are also known as off-line schedulers as these schedulers fix the schedules before the system starts. Table Driven and Cyclic scheduling are two commonly known algorithms under this category [47].

- (b) Event driven: These schedulers dynamically schedule tasks at run-time where the scheduling points are governed by job invocation and job completion. These schedulers can be preemptive or non-preemptive. A preemptive scheduler could suspend the execution of an already executing task in order to execute a higher priority task. A non-preemptive scheduler will only grant the computing resource on termination of an already executing task. Rate Monotonic (RMA) and Earliest Deadline (EDF) are examples of Event driven scheduling algorithms [54, 29].

A feasible schedule on a single computing resource will not miss any deadline even when all the tasks are running at their WCET. In other words, a feasible uniprocessor schedule is the one that satisfies the following condition

$$U = \sum_{i=1}^{n} \frac{E_i}{D_i} \le 1$$

, where n is the number of tasks [54]

Here, U is the aggregate of task densities of all the tasks scheduled on a computing resource. If we assume  $P_i = D_i$ , then U can be called the aggregate utilization. The preemptive Earliest Deadline First (EDF) algorithm obtains this optimality for uniprocessor real-time systems. If U > 1, then the task set cannot be scheduled on a given computing resource. When U < 1, the system is under-utilized and multiple tasks can share the computing resource. This needs multiple real-time tasks to be scheduled by a real-time scheduler that enforces a scheduling policy to share the computing resource.

Most contemporary processors incorporate complex micro-architectural enhancements. Out of order execution [58, 83], branch prediction [99, 100, 82] and speculative execution with value prediction [53, 78] are some of the key features that enable these uniprocessors to deliver high throughput. However, all these features hamper the predictability of WCET for real-time applications, which is the first requirement in order to perform a robust schedulability analysis. Thus, for real-time systems, the focus has been to keep the micro-architecture simple by using in-order processor cores without branch prediction or speculative execution. Another aspect that throttles the throughput is the memory access delay. With higher throughput processors the memory access delay gets worse. Even with lower processor frequency the memory access delays are expensive, e.g., with processor cores running at 700 MHz it takes 70 cycles to access memory for Tilera processors [36]. To reduce memory accesses, on-chip caches are used to store the recently accessed memory locations. For general-purpose computing, cache performance is measured by observing the rate at which the memory references are not found in cache, called the cache miss-rate. The lower the cache miss-rate, the more effective a cache is. The cache miss rate is relevant for assessing the average performance. This information is not sufficient for predictability for real-time systems. Abstract Cache Analysis (ACA) is a mechanism by which the worst-case cache behavior is modeled [71, 79, 68]. Abstract Cache Analysis is incorporated with the aforementioned static analysis tools. Instead of assuming all memory references to cause off-chip memory accesses, an abstract cache is assumed. It is called abstract because the state of a memory address is abstract in this cache. The absolute state of the cache is known only at run-time as it is dependent upon the run-time control flow. However, abstract cache analysis statically analyzes the control-flow graph and determines the abstract state of the cache at any point in the program, which allows one to predict all cache hits that "must" exist regardless of the path taken by the program [89]. Static analysis then follows and calculates the execution time of basic blocks while assuming cache hits for "must" hit references predicted by ACA. Eventually, it converges by determining the WCEP and the WCET. In order to perform ACA, static analysis needs to know some of the key aspects of cache organization.

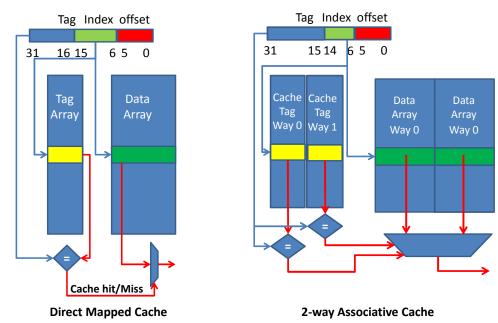

The following are the features of cache organization that will be referred in this dissertation:

1. Cache line: The smallest granularity at which a cache is accessed. Theoretically, cache line

Figure 1.1: Generic view of Cache Architecture

32 KB cache32-bit address64 bytes cache-line size

size can be anywhere from the smallest granularity at which the memory is being accessed to the whole cache size. So, for a 32-bit RISC architecture with 8KB cache may have cache line size from 32 bits to 8KB. However, in practice neither of them are considered suitable. With the former cache line size the spatial locality is sacrificed [43]. Spacial locality suggests that there is a high probability that subsequent memory accesses go to neighboring memory locations. E.g., this behavior is inevitable especially for instruction accesses within a basic block. Having a single cache line is not a good idea either. If only a single cache line is available, then at any time only one block of 8KB can be present in the cache. When a new block is referenced, the new block replaces the older block. If every memory reference refers to different 8KB blocks, then every access will cause a cache miss. Such misses are called conflict cache misses. Thus, cache line sizes in contemporary micro-processors are 32/64 bytes in size [94].

2. Associativity, Cache sets and Cache ways: In order to explain these characteristics, we explain the mechanism by which caches are referenced using a physical memory address. Figure 1.1 shows two types of organizations: A direct-mapped cache and a 2 way set-associative cache. We assume a 32KB cache being accessed by a 32-bit address. We also

assume that 64 bytes as the cache line size. In both the cases, the address is broken into 3 parts:

- (a) Offset: This is used to address the individual bytes within a cache line. Since the number of bytes in a cache line are 64 bytes, the number of bits required to address a 64 byte sized structure is 6 bits. In both cache organizations, the offset uses the low order 6-bits.

- (b) Index: These are the bits that identify if the data corresponding to an address is located in a cache. For a direct-mapped cache, there is room for only one cache line per index. With a 2-way set associative cache, there are two entries per index. The associativity of a direct-mapped cache is 1. It is 2 for a 2-way set-associative cache. The set of locations that are specified by an index in a set-associative cache is called a cache set.  $\log_2 \frac{CacheSize}{Associativity \times Cache \ lineSize}$  number of bits are used as an index.

- (c) Cache tag: The higher order bits left excluding the aforementioned bits are used as the tag. When a cache line is read into a cache, the tag of the cache line is stored in the cache-tag arrays.

When a cache is accessed, the index bits are used to select a cache set in two arrays: the tag array and the data array. Comparisons between the cached tags and the reference tag give us a cache hit/miss signal. On a tag match, it is a cache hit; otherwise, it is a cache-miss. These signals are then used as select lines for the multiplexer that forwards the data corresponding to the tag that has matched. Figure 1.1 shows that our 2-way set-associative cache has 2 memory arrays for tags and 2 memory arrays for data. Each group of memory arrays, i.e., one tag array and its corresponding data array, is called a cache way. A set associative cache is called fully associative when there is a single cache set and any cache line can map within that set. So a 32KB fully associative cache will have a single cache set holding 1024 entries. Usually, fully associative caches are used for smaller cache structures. Also, a 8/16-way set-associative cache approximates a fully associative cache [43]. There are no index bits for fully associative caches because there is only one set and tag bits are all high-order bits excluding offset bits.

3. Cache addressing: The memory address used for addressing a cache can be a physical or virtual address depending upon whether the memory management unit (MMU) for virtualizing memory is used or not. Nearly all implementations of virtual memory divide a virtual address space into virtual pages that map to physical memory regions called the frames. This requires virtual to physical address translation before the physical memory is referenced. A cache can be addressed using either of these addresses. If the virtual address is used then on every context switch, all the contents of the cache need to be flushed. If

a physical address is used with the MMU unit turned on, the translation from virtual to physical address needs to be done prior to accessing the cache. This makes cache access a multiple cycles process. It is worse for real-time systems as dynamic allocation of physical frames to pages makes it impossible to perform ACA as a virtual memory reference can be mapped anywhere in the cache. In high performance systems, the caches are addressed virtually indexed and physically tagged. The virtual indexing allows virtual to physical memory translation to take place in parallel to the retrieval of cache tags and cache lines from indexed cache sets. However, this suffers from aliasing, which happens when some of the bits in the virtual index are changed during translation. In contemporary systems, pages are usually 4KB. A 4KB page can be addressed by using the 12 low-order bits of a given virtual address. These are called page offset bits. The page offset bits remain the same but any of the remaining 20 address bits can be altered during translation. This poses a problem. In Figure 1.1, we see that the index bits went well past the 12th bit. There are several ways to tackle this during run-time but for real-time systems it causes indeterminacy. Since contemporary memories are becoming denser, real-time systems can run with the MMU turned off so that a flat physical memory address is used directly [94]. The physically indexed and physically tagged cache is a viable and predictable option for real-time systems.

- 4. Types of Cache-Misses: When a program starts execution, it does not have any of the program's address space cached. This is a state when the cache is said to be "cold". As the program resumes execution it populates the cache, i.e., the cache becomes "warm". When a cache miss occurs due to accessing a cache line for the first time, it is called a cold or compulsory cache miss. A capacity cache miss occurs if the program's address space does not fit within a given size of the cache. Another form of cache miss is called the conflict cache miss. Conflict cache misses are those that occur in a cache with a given associativity and that could have been prevented by a fully associative cache of same size.

- 5. Replacement Policy: On a cache miss, a new cache line is brought in from memory. In a set-associative cache, a cache miss occurs if all the cache lines in the cache set are marked invalid or none of the valid cached tags match with the address' tag. Invalidations of cache lines occur due to events like cache flushes and invalidations to maintain coherence between processor and I/O devices or between processors on a multicore system (to be described later). If invalid cache lines exist in the indexed set, the incoming cache line is placed there and the cache entry is marked valid. In case all the cache entries are valid, one of the cache entries needs to be replaced. Replacement policy decides which cache line to replace. The replacement policies have widely been studied and proposed. The most commonly used policy is Least Recently Used (LRU). LRU chooses the cache entry

that has been residing in the cache set without being referred for the longest time. The most efficient use of LRU requires a set of counters per cache entry. All the counters need to be updated at every cache hit/miss. This increases the design complexity of caches. Hence, most micro-processor use a pseudo-LRU policy [28]. Locked caches provide some user control over replacement. Locking a cache line prevents a cache line from being replaced. In the context of real-time systems, locked caches have been used for achieving predictability. This is the key reason for cache locking to be prevalent among embedded processors, like the IBMPowerPC 460S,MotorolaMPC7400, Intel 960, ARM940T etc. This will further be discussed in the later chapters.

- 6. Multi-level Caches: One would want to design a large cache structure to reduce cachemisses considerably. Larger caches have higher access time. A processor pipelines instructions to improve throughput but in order to pump a new instruction in the pipeline every cycle, it should be able to read an instruction every cycle. Therefore the cache access latency impacts the critical path of a processor. However, having smaller caches will lead to a higher cache-miss rate. A middle ground is reached with multi-level caches. The cache that is closest to the core processor is called the Level-1 cache or the L1 cache. The farther it goes from the processor, the size and the level of the cache increase. This allows the L1 cache to be smaller and fast enough to match the throughput of the processor. An L2 cache can be larger but is still 1-2 orders of magnitude faster than the memory access latency. Normally, a cache miss at any level leads to an access to the next higher level of cache. By higher level, we mean farther away from the processor. The traversal of a cache line from one level to another is another important aspect of multi-level caches. In an inclusive cache structure, the higher level cache retains the cache line while forwarding the content to the lower level. In contrast, an exclusive cache structure invalidates a cache line at the higher cache level. Inclusive caches are useful as they reduce complexity of cache design. And later in our discussion on multicore cache hierarchy, we will see that it helps in maintaining coherence at a higher cache level. Exclusive caches are capable of using the aggregate cache capacity as they do not maintain additional copies.

- 7. Split and Unified caches: L1 caches are small structures and they are commonly accessed by two different pipeline stages (with the exception of self modifying code). Also, access patterns of instructions are different from that of data. A unified cache holds both instruction and data cache lines. A small unified cache would result in data cache lines and instruction cache lines to evict each other. This phenomenon is known as thrashing. To minimize the thrashing effect and to be able to design caches customized to instruction and data access behavior separately, vendors use split L1 caches (L1 instruction and L1 data cache). Higher-level caches are designed to be unified as they have large capacity.

8. Write-through and Write-back caches: A write-through cache sends updates to its higher levels whenever a cache line is being updated. A write-back cache does not send an update, but updates a dirty bit associated with the cache line instead. Cache lines at higher cache levels get updated when they are evicted from lower levels. If a cache connected to the memory controller is a write-back cache then it considerably reduces the off-chip traffic. We will discuss more pros and cons of these schemes when we discuss multicores in the following section.

Even though the ACA determines lower WCET bounds, with increasing processing demand on real-time systems, task sets might not be schedulable over uni-processors. One of the intuitive mechanisms to improve the throughput of real-time applications would be to increase the processor frequency. Moore's Law has been holding for a long time in microprocessor design, yet single-processor designs have reached a clock frequency wall due to fabrication process and power/leakage constraints [5]. This has led designers to investigate the option of chip multiprocessors (CMPs), a.k.a. multicores, to ensure that performance increases at past rates.

#### 1.2 Multicore Architectures

Application specific cores or accelerators have been used in many embedded systems. In the past decade the advancement in making homogeneous multicore platforms had been the central focus of many micro-processor vendors. Symmetric Multi-Processors (SMPs) were developed with the idea of having multiple processor chips connected via an external shared memory bus, which is used to interface the processors and the memory controller. There are numerous examples of such systems, ranging from the high-end SGI Power Challenge, AMD Opteron, Sun Ultraserver and DEC Alpha Server to the low-end NVidia Tegra and intel Xeon processors. Requests issued by all the cores are serialized on the SMP bus by a bus arbiter. If the cores use a write-through cache, each write would then be sending a request to the memory. This would incur a large amount of traffic that could throttle the performance of all the programs significantly due to lack of memory bandwidth for simple read requests. The other option is to use a write-back cache. This will prevent the updates to go to memory in introducing every time there is an update. This would reduce the traffic but it introduces a problem of a non-coherent view of data. With write-through cache the memory is always coherent with regard to the contents of the caches. And every time an update occurs it becomes visible on the bus. A snoop control unit, which is a part of the cache controller, is responsible for snooping the visible update requests and, in case the updated cache line is present in local cache, then update it. This requires a cache to have one read/write port for local processor requests and another one for the snoop requests. Such a design impedes the performance as a large portion of memory bandwidth is consumed by the update traffic. Modern processors with write-back caches absorb this update traffic but

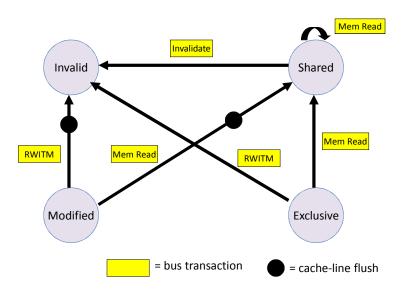

leave memory with stale contents. This also prevents any of the updates to be visible to remote snoop controllers. But it leaves the cache incoherent. In order to ensure coherency, various cache-coherent protocols for SMPs were developed. One of the most common protocols is the MESI protocol. It has four different states that cache lines can be in. The following are the coherency states:

- 1. Modified (M): This means that the cache line is present only in local cache, the contents of the cache line are different from the contents of the memory, and the local processor is permitted to modify the contents.

- 2. Exclusive (E): This state dictates that the cache line is resident only in local cache but its contents are coherent with that in memory. The local processor does not have the right to modify the contents.

- 3. Shared (S): This suggests that there are copies held by remote caches besides the local cache. The contents of the cache line are coherent with memory.

- 4. Invalid (I): The content of the cache line is not valid.

A cache line's state can be modified by local/remote accesses. The memory accesses generated by the local processor are either a read or a write. The key objective of the coherence protocol is to serialize the writes to a cache line (write serialization) and to make the write visible to all the processors (write propagation). This requires a signal to be issued by the cache controller when a local write request finds a cache line in a state other than Modified. We call this signal Read With Intent to Modify (RWITM). When a remote snoop controller snoops an RWITM, it accesses the cache to check if it holds a copy of the cache line. On finding a match, the state of the cache line is transitioned to the Invalid state. If the line in the remote cache is found in Modified state, the contents of the cache line are "flushed". Flushing of a cache line means that the memory is updated with the contents of the cache line. On receiving acknowledgments from all the processors, the snoop controller on the requesting processor updates the state of the cache line to modified and the contents of the cache line are modified.

There are several state transitions that take place due to local and remote requests. Figure 2b shows the state transitions that take place due to locally initiated accesses. The following is a description of the state transitions:

- 1. The cache line is in the Modified State:

- (a) Read Access: Read the contents and stay in the Modified State;

- (b) Write Access: Update the contents and stay in the Modified State.

- 2. The cache line is in the Exclusive State:

- (a) Read Access: Read the contents and stay in the Exclusive State;

- (b) Write Access: Transition to the Modified State and update the contents.

Read Miss(sh) Read Invalid Shared Mem Read Invalidate Read Mem Read RWITM Miss(ex) Write Write Hit Miss Read Read Modified Exclusive Write Hit = bus transaction

Figure 1.2: MESI-Locally Initiated Accesses

#### 3. The cache line is in the Shared State:

Write Hit

- (a) Read Access: Read the contents and stay in the Shared State;

- (b) Write Access: Issue a RWITM bus transaction; on receiving an acknowledgment from the rest of the processors, transition to the Modified State and update the contents.

#### 4. The cache line is in the Invalid State:

- (a) Read Access: This means that the cache line is not present in the local cache. Hence, a mem read bus transaction is issued. When none of the remote caches hold a copy, the state of the cache line is changed to the Exclusive State. If one or more remote caches hold a copy of the cache line then the cache line has to be allocated in the Shared State.

- (b) Write Access: In response to a cache miss, a RWITM bus transaction is issued. The state of the cache line is changed to the Modified State.

Figure 1.3 exhibits the state transitions caused by remotely initiated accesses. The remotely generated bus transactions are RWITM and Mem Read by the cache controllers in response to

Figure 1.3: MESI-Remotely Initiated Accesses

locally generated accesses. As we explained before, the snoop controller snoops the bus at every bus cycle for remote bus transactions. The following is a description of the state transitions caused by the snoop controller:

- 1. The cache line is in the Modified State:

- (a) Mem Read: The state of the cache line switches to Shared State. But this cache line also has the latest updated value, so the contents of the cache line are flushed to update the memory.

- (b) RWITM: The cache line is invalidated and the contents are flushed.

- 2. The cache line is in the Exclusive State:

- (a) Mem Read: The state of the cache line switches to Shared. Note that there is no cache to cache exchange of cache line content. This is because cache-to-cache and memory-to-cache latencies are comparable for SMPs. Thus, the contents can very well be supplied by the memory. However Chip Multi-Processors (CMPs) have on-chip cores connected via an on-chip interconnect. In such architectures, it is efficient to have cache-to-cache transfers.

- (b) RWITM: Invalidate the cache line and the contents are read from memory.

- 3. The cache line is in the Shared State

- (a) Mem Read: The cache line stays in the Shared State

- (b) RWITM: Invalidate the cache line and the contents are read from memory.

- 4. The Cache line is in the Invalid State: This means that remote cache does not hold a copy of the accessed cache line.

Advancement in fabrication technology has enabled vendors to pack a larger number of processor cores with private and shared caches within a single chip. This has motivated researchers to investigate different multi-processor cache structures.

- 1. Shared higher-level caches (like an L2 cache) with coherent lower-level caches (like an L1) that are connected via a coherent bus have been proposed. They have become prevalent in contemporary embedded system designs, e.g., the NVidia Tegra 3 has four ARM processor cores with 32KB L1 Instruction/data caches and a 1MB shared L2 cache [4]. The primary concern looking forward with shared L2 caches is that they do not scale with large numbers of cores. This is due to the coherency traffic as a single RWITM causes all the cores to check their caches and send an acknowledgment. Also, large L2 caches impact the access latency thereby hurting the common case scenario. Large L2 caches contribute to 50% of power dissipation due to leakage current, which contributes significantly to overall power consumption [91].

- 2. Multi-level private caches. The private caches in multi-programmed workloads exhibit lower conflicts and reduced access latency for L2 caches [16]. These processor cores with private L1+L2 caches may be connected via a shared bus or point-to-point interconnects. The Intel Pentium D is an example of such a cache design [2]. For large scale CMPs, processors with mesh interconnects have been in production, e.g., the Tile64Pro from Tilera Corporation. These cores are called tiles. Each tile has private L1+L2 caches and an interconnect router. In a mesh interconnect a tile is connected to its neighbors using a high bandwidth network. The frequency of tile-to-tile transfer typically matches the processor frequency. The routing can also be software controlled and message passing between cores is supported.

- 3. Directory-based caches: A hybrid of the two schemes has also been proposed. The tile based architecture supports a directory-based coherence protocol. A directory entry contains the tag of a cache line and its coherency status. The directory entry also holds an array of bits with each bit representing a tile. A bit value of 1 indicates that the corresponding tile contains a copy of the cache line. There is only one directory entry for each cache line and thus it has to be at a fixed location. Early designs suggested these to be located at the memory controller assuming an on-chip memory controller. But this

would generate a lot of traffic over the interconnect. Like a single shared cache, a single directory becomes an unscalable structure. This motivated the design of a distributed directory. A directory is distributed among tiles. Each cache line has a unique home tile. The home tile of a cache line is dereferenced by certain bits in address similar to the mapping of a cache line to a cache set. Each tile now contains an additional tag array and a corresponding directory entry array. Please note that the home tile can be a remote tile. On a cache miss, a requester tile sends a message to the home tile. Based on the coherency status, additional messages are generated by the home tile to other tiles that hold a copy of the cache line. Those tiles then respond accordingly to the home tile and the requester tile. The Tilera architecture can be configured to support a Private L1+L2 with message passing or a Private L1+L2 with a distributed shared L3 cache.

There has been a substantial amount of research that has improved the average case execution of high performance applications. This has helped multicores to become ubiquitous in several devices that are used on a daily basis, from laptops, cellular phones to supercomputers. However, feasibility of multicores in real-time systems is still under investigation for different cache hierarchies, interconnects and memory interfaces. The following subsections present those reasons in detail.

### 1.3 Multicore Real-time Systems

As the number of tasks increases, the processing demand in terms of overall processor utilization keeps increasing. Thus, a complex system like an automotive subsystem that increases the number of tasks with every new release puts more pressure on computing resources. As discussed before, due to high power leakage with high frequencies, multicores support the execution of multi-programmed workloads. This trend already extends to embedded designs with heterogeneous multicores (e.g., for cell phones) and also homogeneous multicores at a larger scale [6]. Thus, it is evident that multicores will become ubiquitous over the next few years.

#### 1.3.1 Scheduling Real-time Tasks on Multicores

As discussed before, schedulability of a real-time task set is dependent upon the predictability of WCET on a given architecture under a given scheduling policy. In the past decade, several multi-processor scheduling policies have been proposed. These scheduling policies can be widely be characterized as:

1. Static Partitioned Scheduling: Under this type of scheduling, tasks are assigned to a core and are not allowed to migrate [30, 18]. Each core runs an independent scheduler. Though optimal assignment of tasks to partitions has been proven to be an NP-complete problem,

- simple heuristics like first fit decreasing (FFD) have been found to be quite efficient under task partitioning [44]. In Chapter 4, we will be discussing this algorithm in detail.

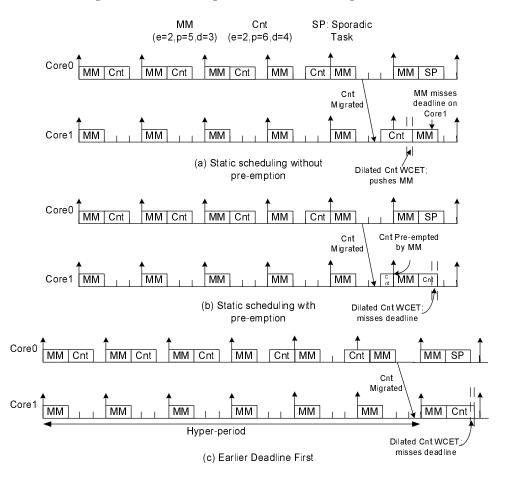

- 2. Global Scheduling: The major drawback with Static Partitioning is that it is unable to distribute tasks that have high density/utilization, i.e., tasks with a utilization greater than 0.5. To address this limitation, global scheduling techniques have been and are being proposed. The fundamental premise of these techniques is that tasks may migrate between cores. Some global scheduling techniques suffer from reduced system utilization [30, 50]. A whole class of fair scheduling algorithms have recently been developed for multicore scheduling that give better utilization bounds [15, 59, 10, 11, 84, 14]. However, under global/fair scheduling it is hard to achieve a tighter bound on the number task migrations. Therefore, these algorithms were proposed as non-work-conserving schedules. A non-work-conserving schedule is one where the computing resource remains idle even though there are tasks ready to be scheduled.

- 3. Semi-Partitioned Scheduling: Another way of limiting the number of task migrations is to use Semi-partitioned scheduling. Here, some of the tasks are statically scheduled while others are allowed to migrate. In such a system, there is a hierarchy of schedulers. There may be a single global scheduler that is invoked at certain events to allocate migratable tasks on different cores. While each core runs an independent scheduler that is responsible for scheduling allocated tasks on a core only. The original work on semi-partitioning was directed at soft real-time systems [12]. Subsequently, several algorithms have been proposed for hard real-time systems [32, 37].

#### 1.3.2 Challenges with Multicore Schedulability

As mentioned in Section 1.3.1, the basic assumption of partitioned/semi-partitioned scheduling is that the tasks are migratable. However, the schedulability analysis for these scheduling policies considers the overhead of task migration to be either zero or some constant value. In order to assume zero migration costs, these algorithms assume processor architectures without any caches, i.e., a memory reference will cause a memory access regardless of the migration. Such an assumption might render tasks unschedulable due to a prohibitively high WCET. Research work conducted upon using caches in multicores has resorted to shared caches. This simplifies the cache analysis as all the tasks are assumed to be sharing a single cache resource. This allows the tasks to have lower utilizations. Pessimistic migration costs are within the allowable range such that the task sets are still schedulable. However, as we have explained, shared caches are unscalable. With increasing processing requirement in every computing domain, including real-time systems, scalable multicore architectures are bound to become ubiquitous. These scalable architectures use private caches. Not much research has been conducted on the usage of private

caches in multicores real-time systems. These assumptions for multicore scheduling algorithms may lead to an inaccurate analysis. Also, static partitioning on scalable multi-processors with private caches have not been studied.

#### 1.4 Problem Statements and Contributions

This dissertation assesses if scalable multicore architectures with private caches are suitable for real-time systems. The following are the issues presented and solutions proposed in this document:

- 1. In Chapter 2, we present a push-assisted cache migration scheme [77]. We illustrate that task migration actually (a) reduces timing predictability for scalable multicores due to cache warm-up overheads while (b) increasing traffic on the network-on-chip (NoC) interconnect. This chapter puts forth a fundamentally new approach to increase the timing predictability of multicore architectures aimed at task migration. A task migration between two cores imposes cache warm-up overheads on the migration target, which can lead to missed deadlines for tight real-time schedules. We propose novel micro-architectural support to migrate cache lines. We present two micro-architectural schemes (a) Whole Cache Migration (WCM) and (b) Regional Cache Migration (RCM). We illustrate that our mechanisms are capable of providing predictable cache migration over a conventional Prefetch Task Model (PTM). Our experimental results show that RCM reduces overheads considerably. This overhead can be steered to fill idle slots in the schedule, i.e., they do not contribute to the execution time of the migrated task. This migration overhead can also be used by schedulers to select migratable tasks during semi-partitioning of task sets [80].

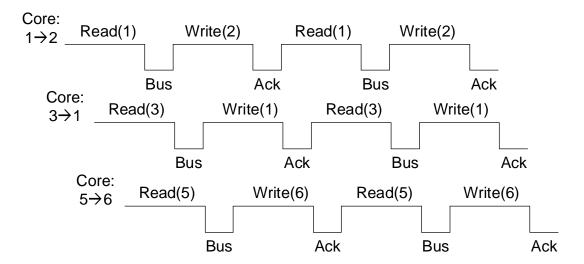

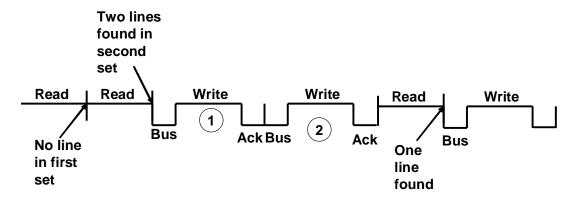

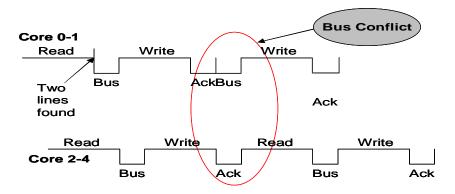

- 2. In Chapter 3, we illustrate the idea of migrating locked cache lines. Locking cache lines in hard real-time systems is a common means of achieving predictability of cache access behavior and tightening as well as reducing worst-case execution time, especially in a multi-tasking environment. Tasks with locked cache lines need to proactively migrate these lines before the next invocation of the task. Otherwise, cache locking on multicore architectures becomes useless as predictability is compromised. This chapter proposes enhancements to hardware-based push-assisted cache migration as a means to retain locks on cache lines across migrations [74]. We improve our RCM and WCM techniques with pipelined cache migration schemes that significantly reduce the cache migration delay of an individual task migration. We also present parallel migration mechanism that maximizes the bus utilization in the midst of multiple cache migrations. We further provide deterministic migration delay bounds that help the scheduler decide which migration

technique(s) to utilize to relocate a single or multiple tasks.

3. In Chapter 4, we further the concept of locked caches on scalable multicore architectures by analyzing its impact on static task partitioning algorithms. In shared cache architectures, a single resource is shared among all the tasks. The objective of task partitioning on a shared cache architecture is to reduce response time of tasks. With scalable architectures, there are abundant computing and cache resources and the focus shifts toward efficiently utilizing computing resources. Also, in scalable cache architectures with private caches, conflicts exist only among the tasks scheduled on one core. This calls for a cache-aware allocation of tasks onto cores. Here, we propose a novel variant of the cache-unaware First Fit Decreasing (FFD) algorithm called the Naive locked First Fit Decreasing (NFFD) policy. We propose two cache-aware static scheduling schemes: (1) Greedy First Fit Decreasing (GFFD) and (2) Colored First Fit Decreasing (CoFFD) for task sets where tasks do not have intra-task conflicts among locked regions (Scenario A) [75]. NFFD is capable of scheduling high utilization task sets that FFD cannot schedule. Experiments also show that CoFFD consistently outperforms GFFD resulting in a lower number of cores and lower system utilization. For a more generic case where tasks have intra-task conflicts, we split task partitioning into two phases: task selection and task allocation (Scenario B) [76]. Instead of resolving conflicts at a global level, these algorithms resolve conflicts among regions while allocating a task onto a core and perform unlocking at the region level instead of the task level. We show that a combination of our novel Dynamic Ordering (task selection) with Chaitin's Coloring (task allocation) scheme reduces the number of cores required considerably over a basic scheme (combination of Monotone Ordering and Regional FFD). Regional unlocking allows this scheme to outperform CoFFD for medium utilization (0.40 > locked task utilization  $\geq$  0.25) task sets from Scenario A. However, CoFFD performs better than any other scheme for high utilization (0.55 > locked task utilization  $\geq$  0.40) task sets from Scenario A.

## 1.5 Hypothesis

Advancement in processor technology provides an opportunity to avail large numbers of computational resources in the form scalable multiprocessors. With the ever increasing computational demand of real-time systems, we foresee the deployment of such systems on scalable multiprocessors. The primary limitation in multiprocessor real-time scheduling is that they are agnostic of private cache organization. Such cache organization results in:

- 1. Unpredictability of task migration costs in global/semi-partitioned scheduling; and

- 2. Ineffective use of computational resources during static partitioning.

We attempt to address these limitation in this dissertation. Hence, the hypothesis of this dissertation is the following:

Multiprocessor real-time scheduling algorithms can more effectively utilize scalable multicore platforms when global/semi-partitioned scheduling techniques predict cache migration costs accurately and static partitioning considers the impact of private caches. Deployment of locked caches and hardware support for cache migration on scalable multi-processors can enable more predictable and efficient multiprocessor real-time scheduling.

## 1.6 Organization

Chapter 2 analyzes the impact of task migration and presents a hardware mechanism for migrating cache lines from one core to another during the slack available within the schedule. Chapter 3 defines the problem of task migration for hard real-time systems using locked cache lines and presents mechanisms to handle individual/multiple cache migrations efficiently. Chapter 4 presents static partitioning mechanisms for private locked caches on scalable multiprocessor architectures. Chapter 5 discusses open problems for future work and presents the conclusions drawn from this work.

## Chapter 2

# Push-Assisted Migration of Real-Time Tasks in Multicore Processors

## 2.1 Timing Predictability and Micro-architectural Challenges

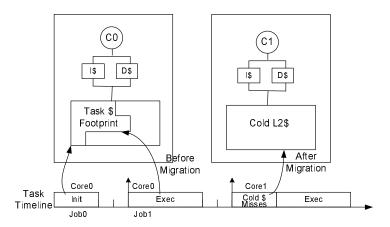

Multicores have been a research topic in micro-architecture, which has led to rapid industry adoption (Intel Core, AMD Barcelona, Sun Niagara, IBM Power) and even advanced scalable multicore designs [5, 6] due to the frequency wall. Past research has focused on improving parallelization strategies [23, 95, 73, 90, 39] to increase average performance and to provide scalability on the memory path [22, 57, 46, 33, 87, 56], including capacity-oriented schemes that scavenge unused neighboring cache lines [34, 24, 26, 101]. Yet, timing predictability actually deteriorates in multicores. Thus the results and inferences drawn from contemporary high-performance computer architecture research are not directly applicable to real-time systems. High performance applications do not have deadlines so that deviations from average performance do not render a system dysfunctional. Real-time systems largely consist of multiple tasks, often periodically scheduled, such that each task is able to meet its deadline. Jobs of a periodic task are then released at regular intervals to obtain sensor readings, perform processing actions of often control-theoretic nature and then engage in actuator actions. Jobs of real-time tasks systems have to complete by their deadline. These jobs require accurate timing predictability to ensure deadlines can be met, which could easily be affected by minor deviations on complex multicore architectures that dilate execution. The dilation of interest in this work is due to migration of a task or an application between processor cores. Task migrations in contemporary architectures are followed by cache warm-ups on the migration target. Cache warm-ups are usually ignored or have insignificant impact for high-performance computing. For example, architectural simulations make use of so-called simpoints, i.e., simulation points that delineate program phases. The idea is to reach a stable architectural state at which average case can be studied [40]. In contrast, cache warm-ups have considerable impact on real-time systems because any dilation in execution time of real-time tasks could lead to system failure.

Multicore research is actively working towards providing scalable multicores with large L2 caches. Distributed shared L2 caches, private L2 caches, and hybrids involving both designs are being actively compared by the high-performance research community. The size of such L2 caches often provides real-time systems with enough resources to fit all tasks within the L2. Consequently, tighter WCETs help tasks to become schedulable by allowing them to meet their deadlines. However, task migrations may cause deadlines to be missed due to dilations in execution time, e.g., due to cache warm-up. Thus task migration on multicore architectures deters the predictability of the WCET of real-time tasks significantly. In order to evaluate the impact of cache warm-ups without any extraneous effects, we simulated a multicore architecture. Our experimental results on the simulated multicore architecture over a set of WCET benchmarks show that task migration can dilate the execution time anywhere from less than a percent to up to 56.6%.

#### 2.2 Introduction

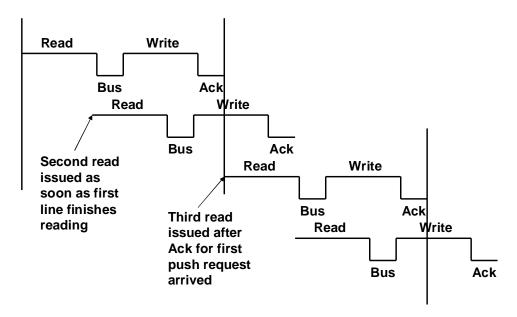

We propose a novel software mechanism to highlight the impact of pro-active migration of cache lines in order to increase the predictability of real time tasks. We follow it up with a novel hardware/software mechanism to dramatically increase predictability in the presence of migration by providing micro-architectural support for task migration that is further suitable for static timing analysis, an area not covered by previous work on WCET analysis for multilevel caches in multicores and shared-memory multiprocessors [60, 98, 42]. In this work we are assuming a multicore architecture with private L1 and L2 caches as explain in the previous chapter. Our solution is based upon transfer of L2 cache lines of a migrated task from a source core to a target core over the coherence interconnect. This migration is initiated between a task's job completion and the next job's invocation, preferably in idle slots of the real-time schedule. Research has been conducted to keep relative deadlines much shorter than periods for tasks in control systems to reduce variation in response time [13, 49]. This leads to composition of tasks with high density but low utilization as shown in Figure 2.2 that also leave idle slots due to slack available in the system. We propose a software scheme, where the scheduler launches a task at the target core that prefetches cache lines. Thus this scheme is called Pre-fetch Task Migration (PTM). It reduces the time dilation to which the task is subjected on the target core as a result of its migration. However, it is not able to prefetch instruction cache lines and imposes high overhead that cannot be reduced. Hence, we investigate a pure hardware scheme,

Figure 2.1: Task Execution amid Task Migration

called Whole Cache Migration (WCM), that restores the whole cache context of the task onto the target core. However, this mechanism involves high overhead, leaving not enough time to migrate all lines before the next job invocation on the target core. Hence, we propose a software assisted hardware scheme, called Regional Cache Migration (RCM), that allows the developer to transfer knowledge about the memory space to be migrated to the cache controller and then initiate a push operation (instead of a pull) of the lines to the target. Thus the cache controller can identify a subset of cache lines subject to migration, which reduces migration overhead. RCM reduces the overhead for all tested benchmarks, for some by an order of magnitude, while constraining the dilation caused by task migration close to the dilation experienced by a task under WCM. The objective of this work is to provide hardware support that enables predictability and reduction in cache-related migration delay (CRMD).

## 2.3 Problem Analysis

This section presents the performance impact of migration of tasks on predictability of their WCET.