### ABSTRACT

MARATHE, JAYDEEP P. METRIC: Tracking Memory Bottlenecks via Binary Rewriting (Under the direction of Assistant Professor Dr. Frank Mueller).

Over recent decades, computing speeds have grown much faster than memory access speeds. This differential rate of improvement between processor speeds and memory speeds has led to an ever-increasing *processor-memory gap*. Overall computing speeds for for most applications are now dominated by the cost of their memory references. Furthermore, memory access costs will grow increasingly dominant as the processor-memory gap widens. In this scenario, characterizing and quantifying application program memory usage to isolate, identify and eliminate memory access bottlenecks will have significant impact on overall application computing performance.

This thesis presents *METRIC*, an environment for determining memory access inefficiencies by examining access traces. This thesis makes three primary contributions. First, we present methods to extract partial access traces from running applications by observing their memory behavior via dynamic binary rewriting. Second, we present a methodology to represent partial access traces in constant space for regular references through a novel technique for online compression of reference streams. Third, we employ offline cache simulation to derive indications about memory performance bottlenecks from partial access traces. By examining summarized and by-reference metrics as well as cache evictor information, we can pinpoint the sources of performance problems. We perform validation experiments of the framework with respect to accuracy, compression and execution overheads for several benchmarks. Finally, we demonstrate the ability to derive opportunities for optimizations and assess their benefits in several case studies, resulting in up to 40% lower miss ratios.

### METRIC: Tracking Memory Bottlenecks via Binary Rewriting

by

Jaydeep P. Marathe

A thesis submitted to the Graduate Faculty of North Carolina State University in partial satisfaction of the requirements for the Degree of Master of Science in Computer Science

### **Department of Computer Science**

Raleigh

2003

Approved By:

Dr. Vincent Freeh

Dr. Gregory Byrd

Dr. Frank Mueller Chair of Advisory Committee

### Biography

Jaydeep Marathe was born on 28<sup>th</sup> November 1978, in Pune, India. He received his Bachelor of Engineering in Computer Engineering from the University of Pune, India, in 2000. He worked with Pace Soft-Silicon Ltd. as a Software Engineer for a year, before starting graduate studies at the North Carolina State University. With the defense of this thesis, he is receiving the Master of Science in Computer Science degree from NCSU, in July 2003.

### Acknowledgements

I would like to thank Dr. Frank Mueller for his guidance and support during the duration of this project, and especially his insistence on consistent writing and coding styles. I would also like to thank Dr. Vincent Freeh and Dr. Gregory Byrd for being on my advisory committee.

# Contents

| Li       | st of                                 | Figures                                                   | $\mathbf{vi}$ |  |  |  |  |  |  |  |  |  |

|----------|---------------------------------------|-----------------------------------------------------------|---------------|--|--|--|--|--|--|--|--|--|

| 1        | Intr                                  | oduction                                                  | 1             |  |  |  |  |  |  |  |  |  |

|          | 1.1 Conventional Profiling Approaches |                                                           |               |  |  |  |  |  |  |  |  |  |

|          |                                       | 1.1.1 Gprof                                               | 2             |  |  |  |  |  |  |  |  |  |

|          |                                       | 1.1.2 Hardware Performance Counters                       | 2             |  |  |  |  |  |  |  |  |  |

|          |                                       | 1.1.3 Incremental Memory Hierarchy Simulation             | 4             |  |  |  |  |  |  |  |  |  |

|          | 1.2                                   | Motivation and Approach                                   | 5             |  |  |  |  |  |  |  |  |  |

|          |                                       | 1.2.1 METRIC                                              | 5             |  |  |  |  |  |  |  |  |  |

|          |                                       | 1.2.2 Dynamic Binary Rewriting vs. Static Instrumentation | 6             |  |  |  |  |  |  |  |  |  |

|          |                                       | 1.2.3 Partial vs. Complete Traces                         | 6             |  |  |  |  |  |  |  |  |  |

|          | 1.3                                   | Outline                                                   | 7             |  |  |  |  |  |  |  |  |  |

| <b>2</b> | The                                   | METRIC Framework                                          | 8             |  |  |  |  |  |  |  |  |  |

|          | 2.1                                   | Dynamic Binary Rewriting                                  | 8             |  |  |  |  |  |  |  |  |  |

|          | 2.2                                   | Framework Overview                                        | 9             |  |  |  |  |  |  |  |  |  |

|          |                                       | 2.2.1 Target Instrumentation                              | 11            |  |  |  |  |  |  |  |  |  |

|          |                                       | 2.2.2 Trace Generation and Compression                    | 11            |  |  |  |  |  |  |  |  |  |

|          | 2.3                                   | Online Detection of Access Patterns                       | 14            |  |  |  |  |  |  |  |  |  |

|          |                                       | 2.3.1 Space Complexity                                    | 20            |  |  |  |  |  |  |  |  |  |

|          |                                       | 2.3.2 Time Complexity                                     | 20            |  |  |  |  |  |  |  |  |  |

|          |                                       | 2.3.3 Comparison with Previous Work                       | 22            |  |  |  |  |  |  |  |  |  |

|          | 2.4                                   | Cache Simulation and User Feedback                        | 22            |  |  |  |  |  |  |  |  |  |

| 3        | Case Studies                          |                                                           |               |  |  |  |  |  |  |  |  |  |

|          |                                       | 3.0.1 Case Study: Matrix Multiplication (mm)              | 26            |  |  |  |  |  |  |  |  |  |

|          |                                       | 3.0.2 Case Study: Erlebacher ADI Integration              | 32            |  |  |  |  |  |  |  |  |  |

| 4        | Vali                                  | Validation Experiments                                    |               |  |  |  |  |  |  |  |  |  |

|          | 4.1                                   | Experiment 1. Accuracy of Simulation                      | 36            |  |  |  |  |  |  |  |  |  |

|          | 4.2                                   | 4.2 Experiment 2. Compression Rate                        |               |  |  |  |  |  |  |  |  |  |

|          | 4.3                                   | 3 Experiment 3. Execution Overhead                        |               |  |  |  |  |  |  |  |  |  |

| <b>5</b> | Rela                                  | ated Work                                                 | 41            |  |  |  |  |  |  |  |  |  |

| 6  | Conclusions and Future Work | 44 |

|----|-----------------------------|----|

| Bi | bliography                  | 46 |

# List of Figures

| 1.1 | Processor-Memory Performance Gap [16]                                    | 2  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | 3 Stages for Trace-based Simulators [29]                                 | 4  |

| 2.1 | Inserting Instrumentation at a Point                                     | 9  |

| 2.2 | The METRIC Framework                                                     | 10 |

| 2.3 | Example: Representing Regular Access Patterns                            | 12 |

| 2.4 | PRSD Representation                                                      | 15 |

| 2.5 | Flowchart: Processing at each Level                                      | 16 |

| 2.6 | Semantics of is_compatible_sibling & is_compatible_child                 | 17 |

| 2.7 | Illustration of the Compression Algorithm                                | 18 |

| 2.8 | (Continued)Illustration of the Compression Algorithm                     | 19 |

| 2.9 | A Comparison of Our Algorithm with Previous Work                         | 25 |

| 3.1 | Per-Reference Cache Statistics for Unoptimized Matrix Multiply           | 27 |

| 3.2 | Evictor Information for Unoptimized Matrix Multiply                      | 27 |

| 3.3 | Per-Reference Cache Statistics for Optimized Matrix Multiply             | 28 |

| 3.4 | Evictor Information for Optimized Matrix Multiply                        | 29 |

| 3.5 | Contrasted Metrics for Matrix Multiply before and after Optimizations    | 31 |

| 3.6 | Contrasted Metrics for ADI before and after Optimizations                | 33 |

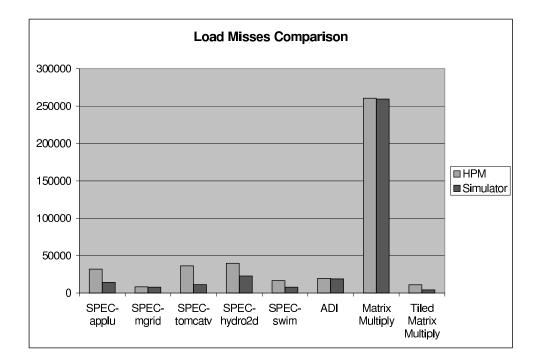

| 4.1 | Comparison of load misses reported by HPM and Cache Simulator $\ldots$ . | 37 |

| 4.2 | Potential Causes of Cache Interference                                   | 38 |

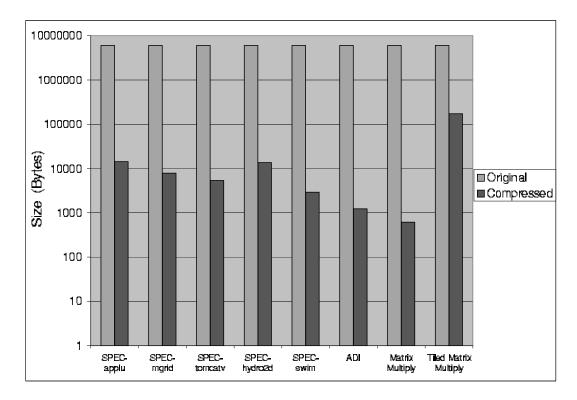

| 4.3 | Comparison of uncompressed and compressed trace sizes                    | 39 |

| 4.4 | Execution Overhead in Target Execution                                   | 40 |

### Chapter 1

## Introduction

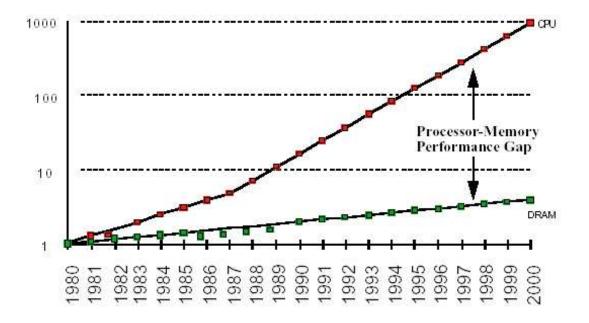

Over recent decades, computing speeds have grown much faster than memory access speeds. Figure 1.1 shows that while micro-processor performance has been improving at a rate of 60% per year, the access time to DRAM has been improving at less than 10% per year [16][27]. This differential rate of improvement between processor speeds and memory speeds has led to an ever-increasing *processor-memory gap*. Memory hierarchies have been introduced to combat this gap; however, overall computing speeds for most applications are still dominated by the cost of their memory references. Furthermore, memory access costs will grow increasingly dominant as the processor-memory gap widens.

In this scenario, characterizing and quantifying application program memory usage to isolate, identify and eliminate memory access bottlenecks will have significant impact on overall application computing performance. This thesis discusses the design, implementation and validation of such a memory profiling tool.

### 1.1 Conventional Profiling Approaches

This section discusses conventional approaches to profiling memory hierarchy usage. We elucidate three broad approaches to the problem, each providing increasingly detailed information about memory hierarchy usage, however with a corresponding increase in the computing and stable storage overheads.

Figure 1.1: Processor-Memory Performance Gap [16]

### 1.1.1 Gprof

Traditional time-based tools to profile application code, such as gprof[14], do not provide direct information about potential memory access bottlenecks. Instead, these tools provide the relative distribution of CPU cycles, over units of the application program, such as functions. It is the responsibility of the programmer to analyze the program units consuming significant CPU cycles, and decide if the memory access patterns are the cause of the excessive CPU cycle consumption. This is a non-trivial task, since memory access bottlenecks can be due to complex interactions of access patterns, which are temporally separated, arising from access points which are dispersed throughout the code.

### 1.1.2 Hardware Performance Counters

Many modern processor architectures provide hardware counters, which can be configured to count specific processor events, such as a data access, a hit or a miss. Several application programming interfaces exist, which allow access to these hardware counters in a portable manner [3][2]. Performance counter based profiling approaches can broadly be classified into *counting* and *sampling* approaches [24].

In the *counting* approach, performance metrics are aggregated for specific regions of the target application source code. Calls to start and stop performance counters are placed selectively around interesting sections of the target application, such as program functions or loop nests. As the application runs, the collected counter values are mapped to the specific program code region being profiled and can also be aggregated to get an overall performance report for the application. This approach requires modifying and recompiling the target application to insert calls to the counter control routines. Calls are placed manually or are inserted automatically by the compiler.

In the *sampling* approach, an "observer" process samples the hardware counters at regular intervals. The observer process can be triggered periodically by a high resolution timer interrupt, or by interrupt on counter overflow, for supporting architectures. An interesting approach [5] uses an n-way search to increase the resolution of sampling. Initially, the entire address range is profiled for cache miss events, using interrupt on counter overflow. Subsequently, different hardware counters are assigned to specific address ranges that show increased rate of misses, thereby identifying memory access bottlenecks. However, this approach requires several advanced hardware features, such as support for partitioning the address space over available counters, which are not widely available in current processor architectures (except the Itanium [10]).

There are several problems with using hardware performance counters to track performance bottlenecks. In the case of memory bottlenecks, the fundamental problem is the *coarse* nature of the statistics, *i.e.*, counter information is useful in highlighting the *symptoms* of memory bottlenecks, but contains insufficient information to diagnose the *cause*. It is left to the programmer to look at the apposite source code fragment and figure out the cause of the bottleneck.

Additionally, in the sampling mode, there is a trade-off between the accuracy of the samples and the rate of sampling. However, an excessive sampling rate can also *perturb* the target application execution, *e.g.*, by cache pollution, thereby affecting the accuracy of results [24]. Furthermore, most hardware architectures have restrictions on the potential events which can be tracked simultaneously, *e.g.*, data cache loads and stores, and it may require multiple runs of the application for different events to get a complete performance breakdown.

### 1.1.3 Incremental Memory Hierarchy Simulation

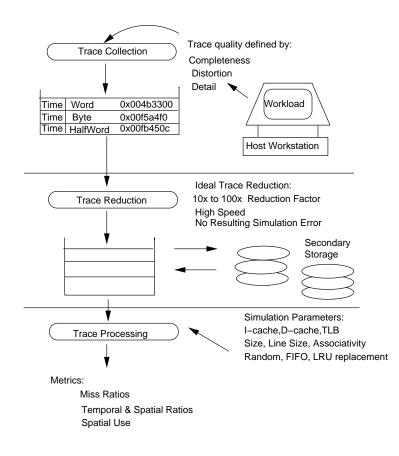

Figure 1.2: 3 Stages for Trace-based Simulators [29]

Memory hierarchy simulators provide a detailed view of a target application's memory hierarchy usage. These simulators use the address trace generated by the target application to do incremental simulation. A comprehensive survey of trace based simulators is presented in Uhlig *et al.* [29]. Figure 1.2 shows the typical stages for these tools - *Trace Collection, Trace Reduction* and *Trace Processing.* Detailed access traces can be extracted at virtually all system levels - from the circuit and microcode level, to the compiler and operating system level [29]. The extracted address traces are relatively large, and they must be effectively compressed for storing on a non-volatile medium, such as the hard disk (*trace reduction*). Finally, the trace data is used for incremental memory hierarchy simulation.

Simulation using address traces has several advantages. Simulations are repeatable and allow cache parameters and data layouts to be varied without regenerating the trace data. They do not require hardware monitoring and access to or the existence of the machine being studied. Most importantly, simulation usually takes place *offline*, *i.e.*, on a separate machine or process, and can therefore afford to maintain more detailed statistics, such as correlation of memory events to source code lines and data structures [23].

However, increased accuracy and level of detail comes at a price. Modern processors are capable of generating gigabytes of data per second, especially on memory intensive applications. Logging the complete access trace to stable storage causes significant degradation in the computing speed of the target application, especially since trace collection has to be done *online*. Storing complete address traces is also problematic, due to the large size of the trace, even with trace reduction.

### **1.2** Motivation and Approach

The last section enumerated different approaches to the task of memory hierarchy profiling. Traditional profiling tools, such as **gprof**, offer no explicit support for profiling memory events. Hardware performance counters provide memory access statistics as they occur in the real physical system and have comparatively low overhead compared to trace-based simulation methods. However, this method provides insufficient information about the underlying *cause* of the memory bottleneck. Additionally, sampling methods represent a trade-off between the rate of sampling and the accuracy of the results as well as the resultant perturbation of the target. Trace-based simulation provides high level of detail potentially correlating access statistics not only to the source code but, more significantly, with the data structures in the program. However, the large size of the complete address trace may cause excessive slowdown of the target application and may have unacceptable stable storage requirements.

In summary, we need detailed cache statistics correlated to program source code and data structures with minimum overhead on target execution and stable storage requirements. The next subsection describes our methodology to achieve these goals.

### 1.2.1 METRIC

This thesis illustrates the use of partial access traces for incremental memory hierarchy simulation, a central component of **METRIC** (**ME**mory **TR**acIing without re-**C**ompiling), a tool we developed to detect memory hierarchy bottlenecks. METRIC exploits *dynamic binary rewriting* by building on the instrumentation framework **DynInst** [4]. Dynamic binary rewriting refers to the post-link time manipulation of binary executables, potentially allowing program transformation even while the target is executing. Partial access traces are collected as the instrumented target resumes execution. We contribute a method for efficient online compression of these partial access traces based on previous work [26]. We also contribute a cache analysis approach, based on prior work [23], that lets us process these partial access traces not only for summary information, such as miss ratios, but also to extract detailed evictor information for source-related data structures.

### 1.2.2 Dynamic Binary Rewriting vs. Static Instrumentation

Dynamic binary rewriting manipulates application binaries at post-link time. This approach is superior to conventional instrumentation, which generally requires compiler interaction (*e.g.*, for profiling) or the inclusion of special libraries (*e.g.*, for heap monitoring), since it obviates the need for recompiling. Run-time binary instrumentation can capture memory references of the entire application, including library routines and mixed language applications, such as commonly found in scientific production codes [30]. Another motivation is its ability to cater to input dependencies and application modes, *i.e.*, changes over time in application behavior. This work is also influenced by findings that binary manipulation techniques offer new opportunities for program transformations, which have been shown to potentially yield performance gains beyond the scope of static code optimization without profile-guided feedback [1].

### 1.2.3 Partial vs. Complete Traces

Traditional trace-based simulators usually require complete access traces. However, a significant problem with this method is the prohibitive overhead of computation and stable storage size requirements of the *complete* address trace, potentially consisting of millions of accesses. *Partial* access traces represent a subset of the access footprint of the target and may be comparatively small and less expensive to collect, allowing selective capturing of the most critical data access points in the target. The METRIC framework allows the user to selectively activate and deactivate tracing, so data streams are being generated or being suppressed, respectively. This facility builds the foundation for capturing partial memory traces.

### 1.3 Outline

The remainder of the thesis is structured as follows. First, we describe the mechanism of dynamic binary rewriting. Next, the METRIC framework is introduced. The target binary instrumentation and the generation of the partial access trace are discussed in detail. We present a new online compression algorithm to efficiently compress the partial access trace. Then, we introduce incremental cache simulation using the partial access traces, and discuss metrics to assess memory throughput. The next chapter presents case studies illustrating the use of the METRIC framework in detecting bottlenecks. Validation experiments comparing the cache simulator statistics against hardware performance counters are presented. Finally, we reflect on related work and summarize our contributions.

### Chapter 2

# The METRIC Framework

This chapter discusses the design of the METRIC framework. First, the technology for dynamic binary rewriting is introduced. Then, an overview of the framework is presented. Later sections describe each phase of the framework in detail.

### 2.1 Dynamic Binary Rewriting

Dynamic binary rewriting refers to the post-link time manipulation of application binaries, allowing program transformation even while the target is executing. Our instrumentation tool is based on DynInst [4], a component middleware design primarily for "debugging, performance monitoring, and application composition out of existing packages". DynInst provides a platform-independent semantics for inserting and manipulating instrumentation code. DynInst has two primary abstractions - *points* and *snippets*. A *point* is a location in a program where instrumentation can be inserted. A *snippet* is a representation of the instrumentation code to be inserted at a point, specified in the form of a platform-independent abstract syntax tree.

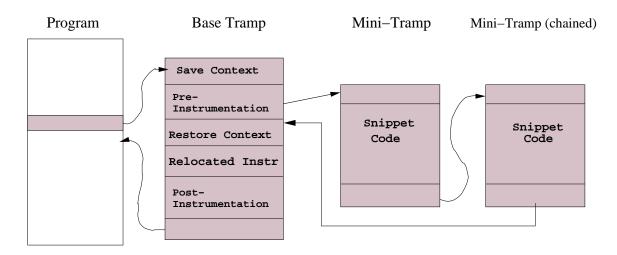

Figure 2.1 shows the mechanics of instrumentation. To instrument a particular point, short snippets of code called *trampolines* are used. The original machine instruction at the instrumentation point is relocated inside the *base trampoline*, and an unconditional branch to the start of the base trampoline is placed at the instrument point location. Since instrumentation can be inserted at arbitrary points in the target binary, the base trampoline saves the complete *machine context* of the target, *i.e.*, the register set contents and the values of the flags in the condition registers. The base trampoline then branches

Figure 2.1: Inserting Instrumentation at a Point

to a *mini-trampoline*, which contains the code for a single instrumentation snippet. Several mini-trampolines can be chained, allowing a sequence of instrumentation snippets. Once the instrumentation code has completed, the base trampoline restores the entire context before executing the relocated instruction. Instrumentation can be placed just before (*pre-instrumentation*) or just after (*post-instrumentation*) the relocated instruction.

### 2.2 Framework Overview

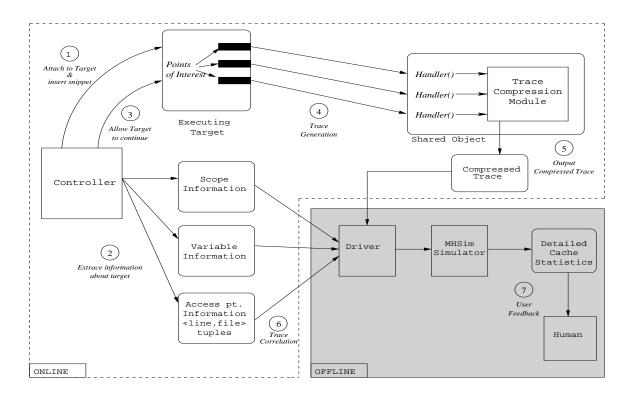

The METRIC framework is shown in Figure 2.2. There are three phases - *target instrumentation, trace generation and compression* and *incremental cache simulation.* The controller process instruments the application binary at points of interest, and collects symbolic correlation information about the target, used later by the cache simulator to correlate results to source program code and data structures. Once the instrumentation is complete, the target is allowed to continue. Instrumentation code calls handler routines which compress the access trace and write the compressed trace to stable storage. One of the central objectives of our work is to capture the memory behavior through partial access traces represented as a subset of the access footprint of an application's execution. Partial access traces are comparatively small, and the executing target has instrumentation overhead only for the duration of collection. Once a specified number of accesses have been logged, or a time threshold has been reached, the instrumentation is removed and the target is allowed to continue. The compressed partial access trace is then used offline

Figure 2.2: The METRIC Framework

for incremental cache simulation. The cache simulator driver reverse maps addresses to variables in the source, using information extracted by the controller, and tags accesses to line numbers. The cache simulator not only generates summary level information, but also reports detailed evictor information for source-related data structures, which is presented to the user for analysis.

In our approach, we exploit source-related debugging information embedded in binaries for correlating results. The application must provide the symbolic information in the binary (*e.g.*, generally by using the -g flag, when compiling). Most modern compilers allow inclusion of symbolic information even if compiling with full optimizations. In particular, IBM's AIX compilers (used for our experiments) and Intel/K&R's compiler for the PowerPC do not suffer in their optimization levels when debugging information is retained. While some debugging information may suffer in accuracy due to certain optimizations, memory references, which are the subject of our study, are not affected. Thus, compiling with symbolic information only increases executable size, without significant degradation of performance.

### 2.2.1 Target Instrumentation

Currently, the user must profile the application using a time-based profiler, such as *gprof*, to determine the hot spot functions. At invocation time of our tool, the user provides the target application process id (PID), and the name(s) of the hot spot function(s) to the control program. The controller uses DynInst to attach to the target, and insert calls to handler functions at points of interest. The handler functions are in a shared library object, which is loaded into the application's address space using a one-shot instrumentation.

For each function, the Control Flow Graph (CFG) is parsed to determine its scope structure. A *scope* is a distinct subdivision used by the cache simulator to report cache statistics. *Loop scopes* encompass natural loops, while *Routine scopes* encompass entire functions. Entry and exit points of scopes are seeded with calls to handler routines. The nesting of the scopes relative to each other is determined. Each scope (except the outermost scope) has a parent scope, and many scopes can have the same parent. The scope nesting enables the cache simulator to aggregate cache statistics.

In addition, the memory access points in the target function are located and seeded with calls to handler routines to trap the generated access trace. DynInst (version 3.0) provides primitives to locate memory access points. To reduce instrumentation overhead, we have augmented the DynInst framework to allow selective instrumentation of memory access points depending on attributes such as the type of data being accessed (*floating point* or *integer*), the byte width of the access point (*byte*, *half-word*, *word* and *double word*), and the source and destination registers (to allow selective logging of only non-stack accesses). Thus, a trade-off is possible between the overhead of instrumentation and the accuracy of the memory hierarchy simulation. This is a very useful feature, since we find that many scientific programs have regular nested loop structures with large number of vector floating point accesses and only a small number of scalar non-floating point accesses. Thus, in these cases, we can safely ignore the scalar accesses with only minor degradation in accuracy of the cache simulator.

### 2.2.2 Trace Generation and Compression

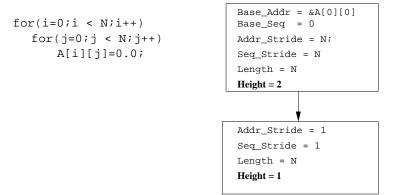

The generation of partial access traces provides the capability to later analyze this trace. Our mechanism is tailored for regular data access patterns, such as those frequently occurring in tight loops. These patterns are represented via *regular section de*-

| <pre>for(i=0;i &lt; n-1;i++) { //begin scope_1 for(j=0;j &lt; n-1;j++)     { //begin scope_2     A[i]=A[i]+B[i+1][j+1     } //end scope_2</pre> | RSD:<br>PRSD:                                                                                                                                                               | PRSD:<br>start_seq_id_seq_id_stride, source_table_index><br>PRSD:<br><br> |                                                                                                                                                                                          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| } //end scope_1                                                                                                                                 |                                                                                                                                                                             |                                                                           |                                                                                                                                                                                          |  |  |

| Event Stream:                                                                                                                                   |                                                                                                                                                                             | to array A:                                                               | Stream Representation:                                                                                                                                                                   |  |  |

| EnterScope1<br>EnterScope2 (j loop)<br>A[0] B[1][1] A[0]<br>A[0] B[1][2] A[0]                                                                   | reads:<br>(i=0) A[0],A[0],<br>(i=1) A[1],A[1],<br>(i=1 to n-2)                                                                                                              |                                                                           | $\begin{array}{l} {\rm RSD1}{<}{\rm A,n-1,0,READ,2,3,1}{>} \\ {\rm RSD2}{<}{\rm A}{+}1,{\rm n-1,0,READ,3n}{+}1,3,1{>} \\ {\rm PRSD1}{<}{\rm A,1,2,3n}{-}1,{\rm n-1,RSD1}{>} \end{array}$ |  |  |

| <br>A[0] B[1][n-2] A[0]<br>ExitScope2<br>EnterScope2 (j loop)                                                                                   | writes:<br>(i=0) A[0], A[0],<br>(i=1) A[1], A[1],<br>(i=1  to n-2)<br>Accesses to array B:<br>reads:<br>(i=0) B[1][1], B[1][2],<br>(i=1) B[2][1], B[2][2],<br>(i=1  to n-2) |                                                                           | $\begin{array}{l} {\rm RSD3{<}A,n{-}1,0,WRITE,4,3,2{>}} \\ {\rm RSD4{<}A{+}1,n{-}1,0,WRITE,3n{+}3,3,2{>}} \\ {\rm PRSD2{<}A,1,4,3n{-}1,n{-}1,RSD3{>}} \end{array}$                       |  |  |

| A[1] B[2][1] A[1]<br>A[1] B[2][2] A[1]<br><br>A[1] B[2][n-2] A[1]<br>ExitScope2                                                                 |                                                                                                                                                                             |                                                                           | $\begin{array}{l} RSD5 < B + n + 1, n - 1, 1, READ, 3, 3, 3 > \\ RSD6 < B + 2n + 1, n - 1, 1, READ, 3n + 2, 3, 3 > \\ PRSD3 < B + n + 1, n - 1, 3, 3n - 1, n - 1, RSD5 > \end{array}$    |  |  |

... ExitScope1

#### Figure 2.3: Example: Representing Regular Access Patterns

scriptors (RSDs) as a tuple <start\_address, length, address\_stride, event\_type, start\_sequence\_id, sequence\_id\_stride,source\_table\_index>, which is an extension of Havlak's and Kennedy's RSDs [15] and are enhancements of prior work[26].

The start\_address, length and address\_stride describe the starting address, number of iterations and strides between successive address values generated by this pattern. The start position of the pattern in the overall event stream is indicated by the start\_sequence\_id, and its interleaving is described by the sequence\_id\_stride. The stride of RSDs may be an arbitrary function. We restrict ourselves to constants in this thesis since we require fast online techniques to recognize RSDs. In different contexts, one may want to consider linear functions or higher order polynomials. Special access patterns are given by recurring references to a scalar or the same array element, which can be represented as RSDs with a constant address stride of zero.

The event\_type distinguishes between reads, writes, enter\_scope and exit\_scope events. For the scope change events, the start\_address field represents the scope id, and the address stride is zero. The source\_table\_index is an index into a table of <filename,line number> tuples. It enables the cache simulator to correlate events with lines in the source code for user feedback.

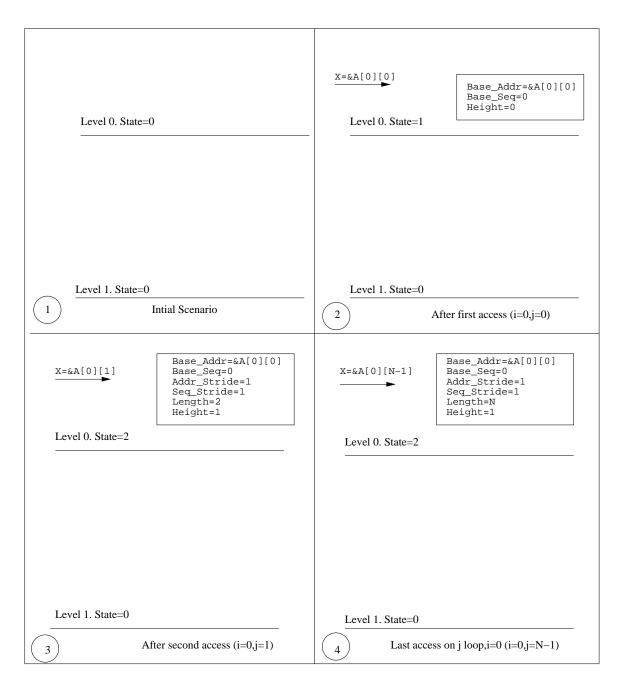

Consider the example with a row-major layout shown in Figure 2.3. For the sake of simplicity, we assume an offset of one per array element. The read references to array B occur at offsets n+1, n+2, n+3 (corresponding to references B[1,1], B[1,2] and B[1,3], respectively), for the first iteration of the outer loop and a length of n-1 accesses. The starting sequence id for the first access of the B array is 3 (since the first three events (seq\_ids start from 0) are the two enter\_scopes for scopes 1 and 2 as well as the read event for A[i]). For one iteration of the outer loop, accesses to the B array occur with an interleave distance of 3 in the overall event stream. Hence, the RSD for array B accesses for 1 iteration of the outer loop is:

RSD5 <B+n+1,n-1,1,READ,3,3,3>

Simple RSDs by themselves are not sufficiently expressive to capture the entire stream of accesses of either array A or B. To address this limitation, we extend this description by *power regular section descriptors (PRSDs)*, which allow the representation of power sets of RSDs as specified in Figure 2.3. A PRSD extends the tuple of an RSD, in that it may contain a PRSD (or RSD) itself, which represents the subset.

The recursive structure of PRSDs provides a hierarchical means to represent recurring patterns with different start addresses but the same strides and lengths. This is useful for patterns that are usually encountered in nested loops.

The example in Figure 2.3 illustrates how all read accesses to array A can be combined as follows:

```

PRSD1: <start_base_address = A,

base_address_shift = 1,

start_base_sequence_id = 2,

base_sequence_id_shift = 3n-1,

PRSD_length = n-1,RSD1>

```

This PRSD represents a total of n-1 repetitions of RSD1 with increments of 1 in

addresses and interleaving distance of 3n-1 between the start of consecutive patterns in the overall event stream.

Events that cannot be classified as a part of a pattern are represented by the *irregular access descriptor (IAD)* as: *<address, type, sequence\_id, source\_table\_index>*. The **sequence\_id** anchors the event in the overall event stream, and the **source\_table\_index** gives the *<*filename,line number> mapping of the instruction causing this event.<sup>1</sup> The type indicates event type (i.e enter / exit scope or load/ store).

Once a specified number of events have been logged or a time threshold has been reached, the instrumentation is removed, and the target is allowed to continue. The compressed description of the event trace (*i.e.*, the PRSDs & RSDs) is written to stable storage.

### 2.3 Online Detection of Access Patterns

This section describes our efficient online algorithm for detecting hierarchical patterns in the access stream. The access stream is segregated by the unique machine code access instruction causing the memory access. Segregation is essential since the incremental cache simulator aggregates statistics by machine code access points as well as source code line numbers, which are derived by mapping the machine access instruction to the source code using the **<filename,line number>** tuples, as explained in the last section. Segregated access streams also exhibit much better regularity, as compared to a "mixed" access stream, since they correspond to accesses generated by the single access instruction, *e.g.*, the access traces for A[i] Read, A[i] Write and B[i+1][j+1] Read in Figure 2.3 exhibit more regularity when the array accesses are considered separately rather than as a single composite access trace.

The compression primitives, *i.e.*, RSDs and PRSDs, are described in the last section. In our algorithm, a pattern is represented as a singly linked list. An example pattern representation is shown in Figure 2.4, assuming each element of array A is of size 1. Each node in the linked list corresponds to a PRSD and has addr\_stride,seq\_stride, length and height fields associated with it. The root node represents the highest level PRSD. The Base\_Addr and Base\_Seq fields of the root node represent the starting address and sequence number for the entire pattern. The height of a node is equal to 1 plus its distance from the leaf node in the PRSD linked list. A node with height 0 (not shown in

<sup>&</sup>lt;sup>1</sup>Line numbers are obtained from debugging information in the binary, as explained earlier.

Figure 2.4: PRSD Representation

figure) is a special entity that represents a pure address element with the fields Base\_Addr and Base\_Seq representing the address value and position in the overall stream, respectively.

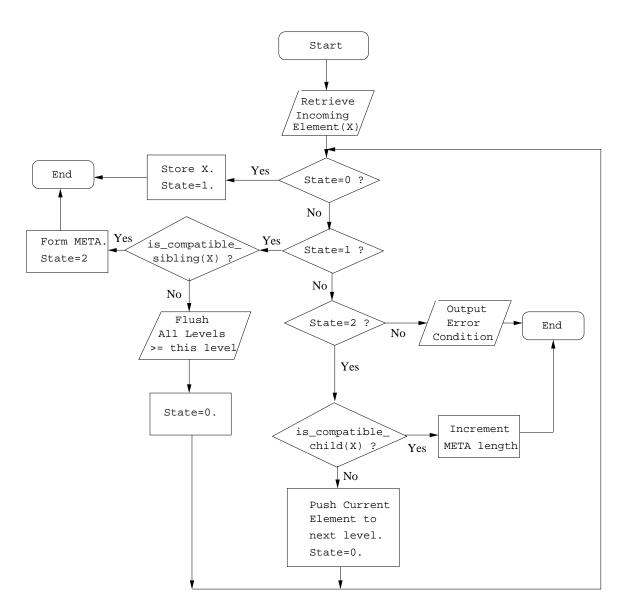

For each access point, we maintain a singly linked list of *levels* with increasing level number starting from 1 for the head node level. Every level can be in three possible states - 0, 1 and 2. State 0 is the default initial state for any level and represents the absence of any element. State 1 indicates that a single PRSD is present with height=level\_number. State 2 indicates the presence of a *meta* element, *i.e.*, a PRSD with height=level\_number+1.

All levels are initially in state 0. As the access stream is processed, hierarchical PRSDs are constructed, and are propagated from lower to higher-numbered levels. Figure 2.5 shows the flowchart of processing for a single level. The instrumentation handlers for memory accesses segregate the incoming access address by the unique machine access instruction initiating the access. For this access point, the compression algorithm is invoked at level 0.

Let X denote the incoming element for a level. For level 0, X represents an access trace element with only the Base\_Addr and Base\_Seq fields valid, while for levels > 0, X is a PRSD.

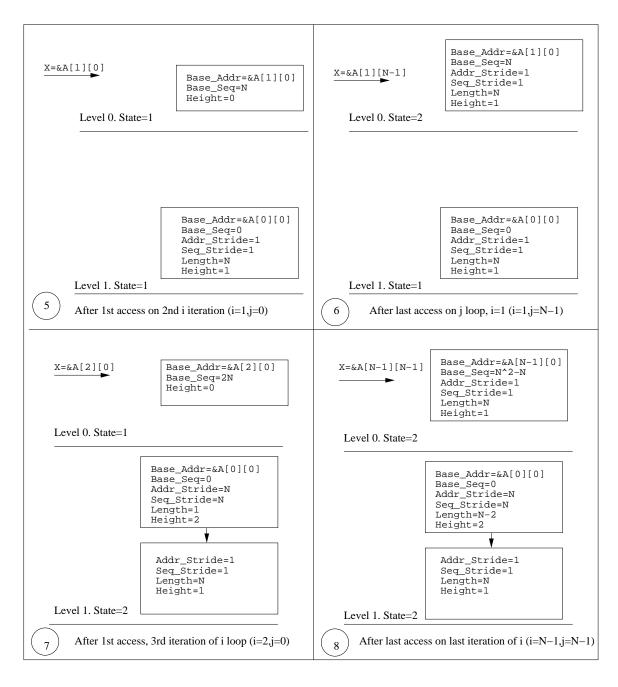

If the level is in state 0, the value of element X is stored (in Y), the level state changes to 1, and processing ends. If the level is in state 1, the is\_compatible\_sibling function checks whether Y (the stored element), and X (the incoming element), are compatible siblings. The semantics of the is\_compatible\_sibling function are shown in Figure 2.6. If the two elements are compatible, a *meta* structure, *i.e.*, a PRSD, is formed and the level state changes to 2. The fields of this PRSD are calculated as follows:

Figure 2.5: Flowchart: Processing at each Level

PRSD.Base\_Addr = X.Base\_Addr

PRSD.Base\_Seq = X.Base\_Seq

PRSD.Length = 2

PRSD.Addr\_Stride = Y.Base\_Addr - X.Base\_Addr

PRSD.Seq\_Stride = Y.Base\_Seq - X.Base\_Seq

PRSD.height = Y.Height + 1

If the two elements are not compatible, it indicates a change in the access pattern of the

access point, and we must flush any existing old patterns. So, all the resident PRSDs in the current level and all higher-numbered levels are flushed to stable storage. Then, the current level moves to state 0 (initial state), and we iterate again with the incoming element X.

| bool is_compatible_sibling(sib1,sib2)            | bool is_compatible_child(parent,child)             |

|--------------------------------------------------|----------------------------------------------------|

| PRSD *sib1, PRSD *sib2                           | PRSD *parent, PRSD *child                          |

| {                                                | {                                                  |

| while(1) {                                       | caddr_t next_addr=0;                               |

| /*1. check each PRSD node in linked list */      | unsigned next_seq=0;                               |

| if $(sib1->length != sib2->length)$              | int dist=0;                                        |

| $   (sib1 > addr_stride != sib2 > addr_stride) $ | int dist=0,                                        |

| (sib1->seq_stride != sib2->seq_stride)           | /*1. check height match $*/$                       |

| (sib1->height != sib2->height))                  |                                                    |

|                                                  | if(parent->height != (child->height+1))            |

| return false;                                    | return false;                                      |

| (*2) : f                                         |                                                    |

| /*2. if reached end, signal success */           | /*2. calculate expected address, sequence id */    |

| if((sib1->child == NULL)                         | dist=parent->addr_stride*(parent->length);         |

| && (sib2->child == NULL) )                       | $next_addr=parent->base_addr+dist;$                |

| return true;                                     | next_seq=parent->base_seq+dist;                    |

|                                                  |                                                    |

| /*3. height mismatch, return failure */          | /*3. check if expected match incoming */           |

| if( $(sib1 - child = NULL)$                      | if( (next_addr $!=$ child->base_addr)              |

| (sib2->child == NULL) )                          | $   (next\_seq != child->base\_seq))$              |

| return false;                                    | return false;                                      |

|                                                  |                                                    |

| /*4. now test for their children */              | /*4. now check lower nodes */                      |

| sib1=sib1->child;                                | return is_compatible_sibling(parent->child,child); |

| sib2=sib2->child;                                |                                                    |

| }                                                | }                                                  |

| }                                                |                                                    |

Figure 2.6: Semantics of is\_compatible\_sibling & is\_compatible\_child

If the level is in state 2, it indicates that a hierarchical PRSD has been formed. The is\_compatible\_child function checks whether the incoming element X is a valid instance of the currently resident PRSD at this level. The semantics of the is\_compatible\_child function are shown in Figure 2.6. If so, then the hierarchical PRSD's length is simply

Figure 2.7: Illustration of the Compression Algorithm

incremented, and processing ends. If X is not a compatible child, the current resident PRSD is pushed to the next level. Then, the current level goes to state 0, and we iterate with the current incoming element X.

Figures 2.7 and 2.8 illustrate the compression algorithm on the C kernel shown in

Figure 2.8: (Continued)Illustration of the Compression Algorithm

Figure 2.3, assuming each array element has size=1 and assuming row-major array layout for simplicity.

The next sections describe the space and time complexity of the compression algorithm.

### 2.3.1 Space Complexity

A purely random sequence without inherent patterns represents the worst case input sequence for space complexity. It takes a linear amount of space to represent such a sequence in our algorithm. Thus worst-case space complexity is O(M), where M is the total number of discrete access events for the particular access point.

A regular access stream generated by a hierarchical loop nest with linear stride functions represents the best case input sequence for space complexity. The amount of space required to represent such a sequence is proportional to the nesting depth  $\mathbf{n}$  of the loop nest under discussion. As the access stream is segregated by the access point, the hierarchical structures (PRSDs) are built separately for each point. Let the maximum number of access points for the loop nest under consideration be  $\mathbf{p}$ . Then, the best case space complexity is  $O(n^*p)$ . Since both  $\mathbf{n}$  and  $\mathbf{p}$  are attributes of the code and are constant for the duration of execution of the application, we have constant space complexity to represent nested loop structures.

### 2.3.2 Time Complexity

Since we must look at all references at least once before compression, the time complexity has a lower bound  $\Omega(M)$ , where M is the total number of discrete access events for the particular access point. The following paragraphs derive the worst case time complexity for the compression algorithm.

Consider the operation of the algorithm as shown in the flowchart in Figure 2.5. It takes a constant number of operations for a particular *level* to transition from state  $0 \rightarrow$  state 1 (operation: storing of incoming element X), and from state  $1 \rightarrow$  state 2 (operation: formation of the *meta* structure). Let these constant number of operations have an upper bound in the constant  $c_1$ .

Consider the compression of accesses produced by the following abstract loop nest:

for(i<sub>1</sub>=0; i<sub>1</sub> < len<sub>1</sub>;i<sub>1</sub>++)

for(i<sub>2</sub>=0; i<sub>2</sub> < len<sub>2</sub>;i<sub>2</sub>++)

....

for(i<sub>n</sub>=0; i<sub>n</sub> < len<sub>n</sub>;i<sub>n</sub>++)

memory\_access(f(

$$i_1$$

, $i_2$ ,..., $i_n$ ));

Since we consider only linear strides,  $f(i_1, i_2, ..., i_n)$  is assumed to be a linear function for the analysis.

Each level  $l_i$  of the algorithm contains hierarchical PRSDs of height i or i+1. For accesses generated by the above loop nest, the height of the representative PRSDs will be bounded by the *nesting depth* of the loop nest, *i.e.*, **n**. This is due to the nature of the PRSD representation as each node in the PRSD linked list corresponds to a particular loop level of the loop nest.

For a particular level  $l_i$ , the is\_compatible\_sibling and the is\_compatible\_child functions must traverse all the nodes in the linked list representation of both the resident PRSD and the incoming PRSD (X). The number of operations for this traversal is on the order of the height of the PRSDs under consideration, *i.e.*, O(n). Then, the exact number of operations (ops) required to compress accesses generated by above loop nest is bounded as:

$$ops \le \sum_{i=1}^{n} (\prod_{j=1}^{i-1}) * (c_1 + t_{is\_compatible\_sibling} + t_{is\_compatible\_child} * (l_i - 2 + 1))$$

$t_{is\_compatible\_sibling} = #$  operations for is\\_compatible\\_sibling function.  $\in O(n)$

$t_{is\_compatible\_child} = #$  operations for is\\_compatible\\_child function.  $\in O(n)$

$c_1 = \text{constant}$  upper bound on # operations for transitions from state  $0 \rightarrow \text{state } 1 \& \text{ state } 1 \rightarrow \text{state}$ 2.

$(c_1 + t_{is\_compatible\_sibling} + t_{is\_compatible\_child}*(l_i-2+1))$  represents the number of operations for one complete execution of the loop at depth i,  $\Pi$  calculates the number of times this occurs. The summation bounds the overall number of operations for the entire loop nest. The expression can be simplified as follows:

$$ops \leq \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) * (c_1 + t_{is\_compatible\_sibling} + t_{is\_compatible\_child} * (l_i - 2 + 1)) (2.1)$$

$$\leq \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) * (c_1 + c_2 * n + c_3 * n * l_i)$$

(2.2)

$$\leq c_1 * \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) + c_2 * n * \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) + c_3 * n * \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) * l_i)$$

(2.3)

Let M be the total number of accesses generated by the loop nest.

$$M = \prod_{k=1}^{n} l_k$$

Using this formula to bound ops, we get:

$$ops \leq c_1 * \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) + c_2 * n * \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) + c_3 * n * \sum_{i=1}^{n} (\prod_{j=1}^{i-1} l_j) * l_i)$$

(2.4)

$$\leq c_1 * \sum_{i=1}^{n} (\prod_{j=1}^{n} l_j) + c_2 * n * \sum_{i=1}^{n} (\prod_{j=1}^{n} l_j) + c_3 * n * \sum_{i=1}^{n} (\prod_{j=1}^{i} l_j)$$

(2.5)

$$\leq c_1 * \sum_{i=1}^n (M) + c_2 * n * \sum_{i=1}^n (M) + c_3 * n * \sum_{i=1}^n (M)$$

(2.6)

$$\leq (c_1 + c_2 * n + c_3 * n) * M * \sum_{i=1}^{n} (1)$$

(2.7)

$$\leq M * (c_1 + c_2 * n + c_3 * n) * \frac{n * (n+1)}{2}$$

(2.8)

Thus, the growth class is:

$$ops \in O(M * n^3)$$

Since  $\mathbf{n}$ , *i.e.*, the nesting depth, is constant and usually quite small, the algorithm has worst case time complexity linear in the total number of references, M.

### 2.3.3 Comparison with Previous Work

Mueller *et. al* [26] introduced the **PRSD**, **RSD** and **IAD** compression primitives. They also presented an online compression scheme to compress partial access traces. We compare and contrast our algorithm with this compression scheme in Figure 2.9.

### 2.4 Cache Simulation and User Feedback

The compressed event trace is used for off-line incremental cache simulation. We use a modified version of MHSim [23] as the cache simulator. MHSim was designed "to identify source program references causing poor cache utilization, quantify cache conflicts, temporal and spatial reuse, and correlate simulation results to references and loops in the source code".

The original MHSim package used a source-to-source Fortran translator to instrument data accesses with calls to the MHSim cache simulation routines. However, this strategy has several disadvantages. Data accesses specified in the source code are simulated in their canonical execution order, ignoring any compiler transformations that may change the order of accesses. Additionally, the compiler may eliminate several accesses during optimizations (*e.g.*, common sub-expressions). We avoid these problems by instrumenting the application binary instead of the application source. The event trace describes the order of accesses as they occurred during execution. The cache simulator driver uses the application symbol table to reverse map the trace addresses to variable identifiers in the source. It relies on the symbolic information embedded in the binary, as explained before. Every compressed trace representation (*i.e.*, PRSDs, RSDs and IADs) has an associated "source\_table\_index", which indexes into a table of <filename,line number> tuples correlating the access instruction in the binary to the source level access that it represents. MHSim is capable of simulating multiple levels of memory hierarchy. However, we concentrate our analysis only on the first level of cache (*i.e.*, L1 cache).

For each access point, MHSim provides:

- total hits associated with the reference.

- total misses associated with the reference.

- miss ratio for the reference: basic factor in evaluating locality of reference.

- temporal reuse fraction for the reference, *i.e.*, the number of  $\frac{temporal hits}{total hits}$ : Useful for determining how much locality (temporal and spatial) the reference is providing. This can be checked against the source code to see how much potential for locality the reference actually has.

- **spatial use**, which is computed as  $\frac{used \ bytes}{block \ size \ * \ \# \ evictions}$ , gives an indication of the fraction of the cache block being referenced before an eviction occurs. A low spatial use count would indicate that the machine is wasting cycles and/or space bringing in data that is never referenced.

- evictor references: the identities of the competing references which evicted this reference from the cache, and their relative counts. These are useful for determining

which data objects conflict with each other. The conflict can be resolved by program transformations or by data reorganization (e.g., array padding).

| Our Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Previous Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Description <ul> <li>Access traces segregated by access point.</li> </ul> </li> <li>Every access point is associated with numbered <i>levels</i>; a level l<sub>i</sub> can contain a PRSD of height i or i+1.</li> <li>PRSDs are propagated from lower to higher-numbered levels where they combine to form higher order PRSDs.</li> </ul>                                                                                                                                                                                                                                 | <ul> <li>Description <ul> <li>Maintain pool table, a block of addresses to be compressed.</li> </ul> </li> <li>A difference table calculates differences between pool elements; RSDs are located by finding sequence of pool elements with identical difference values.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

| <b>Ordering of Accesses</b><br>Globally unique <i>sequence_ids</i> are associ-<br>ated with each PRSD, ensuring global or-<br>dering and interleaving among all pat-<br>terns.<br><b>Time Complexity:</b> $O(M \ge n^3)$<br>M = total # accesses<br>n = nesting depth of loop nest                                                                                                                                                                                                                                                                                                   | Ordering of Accesses<br>Two streams are ordered relative to each<br>other, using the <i>interleave vector</i> (IV). The<br>two streams, plus the IV, forms the <i>data</i><br><i>stream</i> (DS), which can be further ordered<br>relative to others data streams using IVs.<br>Time Complexity: $O(M \times w^2)$<br>M = total # accesses<br>w = width of pool table<br>(Time complexity only for RSD detection)                                                                                                                                                                                                                                                 |

| <ul> <li>Space Complexity:<br/>O(M), Ω(n*p)</li> <li>M = total # accesses</li> <li>n = nesting depth, p = # access pts.</li> <li>Pros</li> <li>Since n is a small constant, worst case time complexity linear in the total number of references.</li> <li>Provides access point segregated access traces; essential for correlating memory statistics to source code.</li> <li>Cons</li> <li>Potential compression using pattern regularity across access points is lost, due to stream segregation</li> <li>Current algorithm considers access with only linear strides.</li> </ul> | <ul> <li>Space Complexity:<br/>O(M), Ω(n)</li> <li>M = total # accesses</li> <li>n = nesting depth</li> <li>Pros</li> <li>Trade-off possible between compression overhead and level of compression, by varying the pool width w.</li> <li>Since access streams are not segregated, can exploit pattern regularity across access points, resulting in potentially improved compression.</li> <li>Cons</li> <li>Cannot be used for METRIC, since accesses from different access points are not distinguished.</li> <li>Potentially slower, since the composite access stream rather than the access-point-segregated stream must be scanned for patterns</li> </ul> |

Figure 2.9: A Comparison of Our Algorithm with Previous Work

### Chapter 3

## Case Studies

In this chapter, we illustrate the use of our framework to analyze the locality behavior of several test kernels. We show how the cache simulation results can be used to detect and isolate bottlenecks and to derive appropriate program transformations.

The cache configuration had the following parameters: cache size of 32 KB, 32byte line size, 2-way associativity, LRU cache replacement policy. A partial data trace was obtained for each kernel. The compressed trace was run through the cache simulator to produce memory hierarchy statistics.

### 3.0.1 Case Study: Matrix Multiplication (mm)

We first report on experiments with a matrix multiplication kernel. The C source code is shown below (assuming that arrays are row-major).

60 for (i=0; i < MAT\_DIM; i++)

61 for (j = 0; j < MAT\_DIM; j++)

62 for (k = 0; k < MAT\_DIM; k++)

63 x[i][j]=y[i][k]\*z[k][j]+x[i][j];

MAT\_DIM = 800

total memory accesses logged = 1000000</pre>

The order of accesses is important to distinguish two different source code references to the same array in the report statistics (for example, x[i][j] READ and x[i][j]WRITE). In the report tables, each distinct reference point from the machine code is represented by an identifier composed of the name of the data object it refers to, appended with the type of access (READ/WRITE) and the position of the reference point in the

|      |      |            |                                      |                       |                       | Miss                   | Temporal | Spatial   |

|------|------|------------|--------------------------------------|-----------------------|-----------------------|------------------------|----------|-----------|

| File | Line | Reference  | Source_Ref                           | Hits                  | Misses                | $\operatorname{Ratio}$ | Ratio    | Use       |

| mm.c | 63   | z_Read_1   | z[k][j]                              | 0                     | $2.50\mathrm{e}{+05}$ | 1.00                   | no hits  | 0.171     |

| mm.c | 63   | y_Read_0   | $\mathbf{y}[\mathbf{i}][\mathbf{k}]$ | $2.39\mathrm{e}{+05}$ | 1.10e + 04            | 0.0441                 | 0.854    | 0.129     |

| mm.c | 63   | $x_Read_2$ | x[i][j]                              | $2.50\mathrm{e}{+05}$ | $1.57e{+}02$          | 0.0006                 | 1.00     | 0.5       |

| mm.c | 63   | x_Write_3  | x[i][j]                              | 2.50e+05              | 0.0                   | 0.0                    | 1.00     | no evicts |

Figure 3.1: Per-Reference Cache Statistics for Unoptimized Matrix Multiply

| Reference |      |           |               |      | Evictors |                                  |                                      |                               |                              |

|-----------|------|-----------|---------------|------|----------|----------------------------------|--------------------------------------|-------------------------------|------------------------------|

| File      | Line | Name      | $Source\_Ref$ | File | Line     | Name                             | Source_Ref                           | Count                         | Percent                      |

| mm.c      | 63   | y_Read_0  | y[i][k]       | mm.c | 63       | z_Read_1                         | z[k][j]                              | 10863                         | 100.00                       |

| mm.c      | 63   | z_Read_1  | z[k][j]       | mm.c | 63       | z_Read_1<br>y_Read_0<br>x_Read_2 | y[i][k]                              | <b>238150</b><br>10854<br>149 | <b>95.58</b><br>4.36<br>0.06 |

| mm.c      | 63   | x_Read_2  | x[i][j]       | mm.c | 63       | z_Read_1                         | $\mathbf{z}[\mathbf{k}][\mathbf{j}]$ | 149                           | 100.00                       |

| mm.c      | 63   | x_Write_3 | x[i][j]       | mm.c | 63       | z_Read_1                         | $\mathbf{z}[\mathbf{k}][\mathbf{j}]$ | 149                           | 100.00                       |

Figure 3.2: Evictor Information for Unoptimized Matrix Multiply

overall order of accesses in the binary. (For example, in the untiled matrix multiply kernel's machine code, the order of accesses is y(read), z(read), x(read), x(write) indicated as y\_Read\_0, z\_Read\_1, x\_Read\_2 and x\_Write\_3, respectively.) We observe the following overall performance:

| miss ratio | = | 0.26119 | spatial use    | = | 0.16980 |

|------------|---|---------|----------------|---|---------|

| misses     |   |         | spatial ratio  | = | 0.04721 |

| hits       | = | 738811  | temporal ratio | = | 0.95279 |

| writes     | = | 250000  |                |   | 34881   |

| reads      | = |         | temporal hits  |   | 703930  |

|            |   |         |                |   |         |

The high miss rate (26%) should be the first indication of concern for the analyst. Interestingly, the spatial use value is quite low (0.16980). This indicates that the current program referencing order is inefficient in the sense that most cache blocks are being evicted before the entire data in the block is referenced at least once.

Let us explore the cache statistics at a higher level of detail. Refer to Figure 3.1

|      |      |           |                                      |                       |            | Miss   | Temporal | Spatial   |

|------|------|-----------|--------------------------------------|-----------------------|------------|--------|----------|-----------|

| File | Line | Reference | Source_Ref                           | Hits                  | Misses     | Ratio  | Ratio    | Use       |

| mm.c | 86   | x_Read_2  | x[i][j]                              | 2.41e + 05            | 8.79e + 03 | 0.0352 | 0.972    | 0.673     |

| mm.c | 86   | y_Read_0  | $\mathbf{y}[\mathbf{i}][\mathbf{k}]$ | $2.41e{+}05$          | 8.79e + 03 | 0.0352 | 0.896    | 0.732     |

| mm.c | 86   | z_Read_1  | $\mathbf{z}[\mathbf{k}][\mathbf{j}]$ | 2.50e+05              | 2.88e + 02 | 0.0011 | 0.999    | 0.861     |

| mm.c | 86   | x_Write_3 | x[i][j]                              | $2.50\mathrm{e}{+05}$ | 0.00e+00   | 0.0    | 0.989    | no evicts |

Figure 3.3: Per-Reference Cache Statistics for Optimized Matrix Multiply

for the per-reference cache statistics. The  $z\_Read\_1$  performance is immediately striking. All accesses to the z array were misses. A look at the source indicates the cause: The k loop runs over the rows of z. By the time reuse of z data occurs (on next iteration of the i loop), the data has been flushed from the cache. With only a single element of the cache line containing z being referenced for each iteration of k, the spatial use value is also low (0.171).

With the x\_Read\_2 reference, the number of hits is large, as expected, since the x[i][j] read is invariant for the k loop. Even here, however, the spatial use is low (0.5) indicating premature eviction before all data in the block was referenced. The x\_Write\_3 writes to data locations already brought into cache by the x\_Read\_2 reference, explaining a miss rate of 0.

For the y\_Read\_0 reference, the number of hits is quite large, comparable in magnitude to the hits for the x\_Read\_2 reference. A surprising feature is the relatively high temporal ratio (0.854). With the k loop running over the column dimension of y and temporal reuse not occurring till next iteration of j, we would rather expect the temporal fraction of hits to be low. This means that the y\_Read\_0 reference does not experience too much interference from other references over long stretches of accesses (more than the length of the k loop).

The evictor table for mm is shown in Figure 3.2. Again, the z\_Read\_1 reference performance is unusual. Over 95% of the time, z\_Read\_1 interfered with itself, indicating a capacity problem. Additionally, z\_Read\_1 was the evictor for all the other references (100% of the time). These evictions by z cause premature invalidation of block data belonging to evicted references, leading to low spatial use (and, thus, low overall cache usage efficiency) for these references.

Improving data locality: We have pinpointed the z array references as having

|      |      | Reference  |                                      |                 |      | Evicto       | rs                                   |                        |         |

|------|------|------------|--------------------------------------|-----------------|------|--------------|--------------------------------------|------------------------|---------|

| File | Line | Name       | Source_Ref                           | File            | Line | Name         | $Source\_Ref$                        | $\operatorname{Count}$ | Percent |

| mm.c | 86   | $z_Read_1$ | z[k][j]                              | mm.c            | 86   | y_Read_0     | y[i][k]                              | 100                    | 69.44   |

|      |      |            |                                      | $\mathrm{mm.c}$ | 86   | $x_Read_2$   | x[i][j]                              | 42                     | 29.17   |

|      |      |            |                                      | mm.c            | 86   | $z_Read_1$   | $\mathbf{z}[\mathbf{k}][\mathbf{j}]$ | <b>2</b>               | 1.39    |

|      |      |            |                                      |                 |      |              |                                      |                        |         |

| mm.c | 86   | $x_Read_2$ | x[i][j]                              | $\mathrm{mm.c}$ | 86   | $x_Read_2$   | x[i][j]                              | 4976                   | 60.05   |

|      |      |            |                                      | mm.c            | 86   | $y_{Read_0}$ | y[i][k]                              | 3297                   | 39.79   |

|      |      |            |                                      | $\mathrm{mm.c}$ | 86   | $z_Read_1$   | $\mathbf{z}[\mathbf{k}][\mathbf{j}]$ | <b>14</b>              | 0.17    |

|      |      |            |                                      |                 |      |              |                                      |                        |         |

| mm.c | 86   | x_Write_3  | x[i][j]                              | $\mathrm{mm.c}$ | 86   | $x_Read_2$   | x[i][j]                              | 4976                   | 60.05   |

|      |      |            |                                      | $\mathrm{mm.c}$ | 86   | y_Read_0     | y[i][k]                              | 3297                   | 39.79   |

|      |      |            |                                      | $\mathrm{mm.c}$ | 86   | $z_Read_1$   | $\mathbf{z}[\mathbf{k}][\mathbf{j}]$ | <b>14</b>              | 0.17    |

|      |      |            |                                      |                 |      |              |                                      |                        |         |

| mm.c | 86   | $y_Read_0$ | $\mathbf{y}[\mathbf{i}][\mathbf{k}]$ | $\mathrm{mm.c}$ | 86   | y_Read_0     | y[i][k]                              | 5010                   | 59.52   |

|      |      |            |                                      | $\mathrm{mm.c}$ | 86   | $x_Read_2$   | x[i][j]                              | 3279                   | 38.96   |

|      |      |            |                                      | mm.c            | 86   | z_Read_1     | z[k][j]                              | 128                    | 1.52    |

Figure 3.4: Evictor Information for Optimized Matrix Multiply

the maximum effect on cache performance. We need to change the program structure to reduce the access footprint for z. By interchanging the j and k loops, we can increase locality for z (since now the inner loop runs over the columns of z), which has the highest number of misses. By strip mining the j and k loops, we can force the temporal reuse to occur at shorter intervals in the overall event stream, especially for arrays y and x. This will reduce the chance of these references having blocks flushed from the cache before the entire block data is utilized. The new transformed code with these improvements is shown below.

```

81 for (jj=0; jj<MAT_DIM; jj += ts)

82 for (kk=0; kk<MAT_DIM; kk += ts)

83 for (i=0; i<MAT_DIM; i++)

84 for (k=kk; k<min(kk+ts,MAT_DIM); k++)

85 for (j=jj; j<min(jj+ts,MAT_DIM); j++)

86 x[i][j]=y[i][k]*z[k][j]+x[i][j];

tile size ts = 16;</pre>

```

We observe the following overall performance:

| miss ratio | = | 0.01787 | spatial use    | = | 0.70394 |

|------------|---|---------|----------------|---|---------|

| misses     | = | 17872   | spatial ratio  | = | 0.03559 |

| hits       | = | 982128  | temporal ratio | = | 0.96441 |

| writes     | = | 250000  | spatial hits   | = | 34955   |

| reads      | = | 750000  | temporal hits  | = | 947173  |

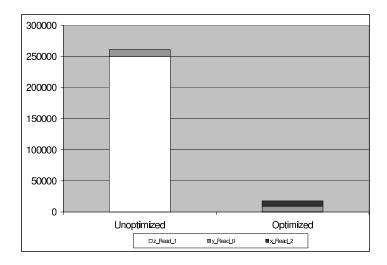

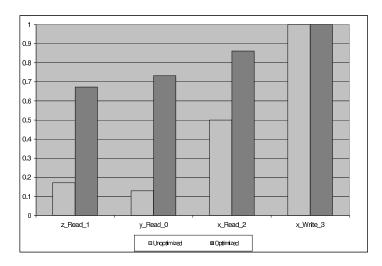

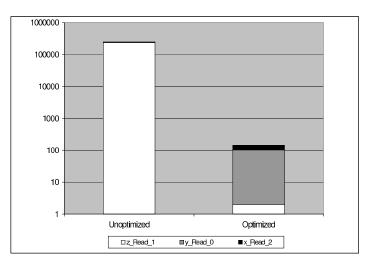

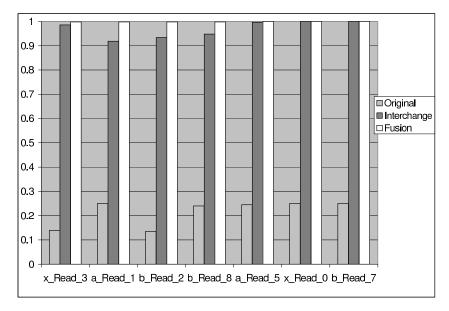

Figures 3.3 and 3.4 show the per-reference cache statistics and the evictor table for the transformed matrix multiply code. Figures 3.5(a-c) contrast the results before and after optimization for misses, use and evictor information for the critical reference z\_Read\_1, respectively.

The overall miss ratio has decreased two orders of magnitude from 0.26 to 0.017. The overall spatial use has also improved greatly from 0.16980 to 0.70394. The greatest improvement has occurred for the  $z_Read_1$  reference; the number of hits has gone down from 0 to 2.5e+05, with 99.9% of these being temporal hits.

Also, for all references, the spatial use values have gone up, increasing the efficiency of cache usage. The eviction table in Figure 3.4 why this happened. The number of evictions for most references has gone down significantly, especially for the z reference from almost 240,000 to less than 200. Evictors for this reference are also depicted in Figure 3.5(c). For other references, the evictors are mostly references to the same array. Overall, the interference between the z reference and other references has been significantly reduced with a slight overall increase in interference between other references (*e.g.*, between y\_Read\_0 and x\_Read\_2).

Consider the pseudo-code for the unoptimized matrix multiply again. Two references to  $\mathbf{x}$ , a read and a write, are inflicted on one array element. We performed our experiments by compiling without allocating  $\mathbf{x}[\mathbf{i}][\mathbf{j}]$  to a register in the inner loop. While register allocation would have affected the total number of references for  $\mathbf{x}$ , it has a negligible impact on eviction and miss ratios, as verified by the low eviction count of 149 in Figure 3.2. Only one out of 800 array references would have been affected in arrays  $\mathbf{y}$  and  $\mathbf{z}$ . In the optimized case, allocating  $\mathbf{y}$  to a register would have had a similar affect since the cache associativity was two and both tiled blocks of  $\mathbf{x}$  and  $\mathbf{y}$  could co-exist in cache.

(a) Total Number of Misses

(b) Spatial User per Reference

<sup>(</sup>c) Evictors for z\_Read\_1 (log scale)

Figure 3.5: Contrasted Metrics for Matrix Multiply before and after Optimizations

#### 3.0.2 Case Study: Erlebacher ADI Integration

The C kernel for the Erlebacher ADI Integration is shown below. For this kernel, the possible optimizations (loop interchange and fusion) are visually apparent. However, we illustrate how the cache results can be used to divine the need for these optimizations. The result analysis would be similar in the case of more non-obvious codes benefiting from the same loop optimizations.

16 for (k = 1; k < N; k++) {

17 for (i = 2; i < N; i++)

18 x[i][k] = x[i][k] - x[i-1][k]\*a[i][k] /b[i-1][k];

19 for (i = 2; i < N; i++)

20 b[i][k] = b[i][k] - a[i][k] \* a[i][k] /b[i-1][k];

21 }

N = 800

total memory accesses logged = 1000000</pre>

We observe the following overall performance:

| reads      | = | 800000 | temporal hits  | = | 351731  |

|------------|---|--------|----------------|---|---------|

| writes     | = | 200000 | spatial hits   | = | 147768  |

| hits       | = |        | temporal ratio |   |         |

| misses     | = | 500501 | spatial ratio  | = | 0.29583 |

| miss ratio | = |        | spatial use    |   | 0.20181 |

As in mm, the primary indicator of concern is the miss ratio — over 50% of the total accesses are misses. Spatial hits constitute just a third of the overall hits. The low spatial use value (0.20) indicates the poor efficiency of the current program order of memory accesses.

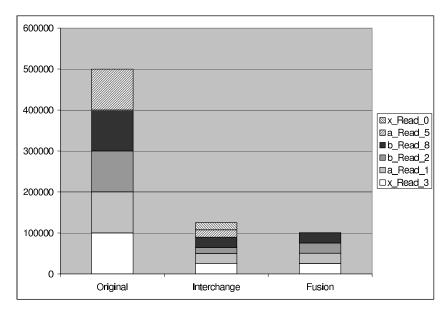

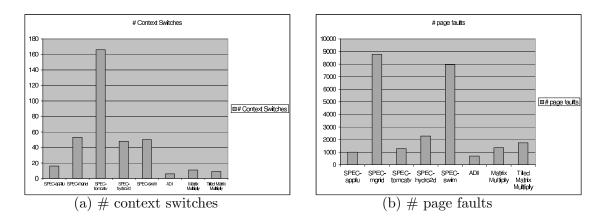

The reference-specific statistics are summarized in the first bar of Figure 3.6(a). In addition, Figure 3.6(b) indicates low spatial use for read references in the original code. The first five references x[i][k], a[i][k], b[i-1][k], b[i][k] and a[i][k] do not have a single hit in the cache. Looking at the source code, a common pattern is evident among all these reference: the inner loop (i loop) runs over the rows of these references. Spatially adjacent elements from these arrays, in the same cache block as these references, are accessed only on the next iteration of the k loop, by which time they have been flushed from the cache. Hence, spatial use value is low, and spatial hits are negligible.

The evictor information (not shown due to its size) actually indicates this problem independent of source code knowledge. A circular dependency exists for the references and

(a) Total Number of Misses

(b) Spatial User per Reference

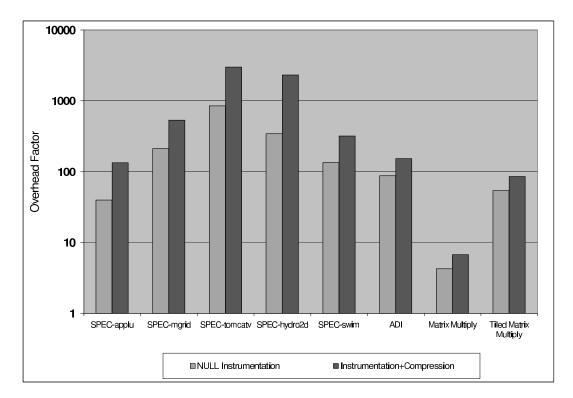

Figure 3.6: Contrasted Metrics for ADI before and after Optimizations