# **METRIC:** Memory Tracing via Dynamic Binary Rewriting to Identify Cache Inefficiencies

JAYDEEP MARATHE, FRANK MUELLER

North Carolina State University

TUSHAR MOHAN

IBM India Research Lab

SALLY A. MCKEE

Cornell University

BRONIS R. DE SUPINSKI, ANDY YOO

Lawrence Livermore National Laboratory

With the diverging improvements in CPU speeds and memory access latencies, detecting and removing memory access bottlenecks becomes increasingly important. In this work we present METRIC, a software framework for isolating and understanding such bottlenecks using partial access traces. METRIC extracts access traces from executing programs without special compiler or linker support. We make four primary contributions. First, we present a framework for extracting partial access traces based on dynamic binary rewriting of the executing application. Second, we introduce a novel algorithm for compressing these traces. The algorithm generates constant space representations for regular accesses occurring in nested loop structures. Third, we use these traces for offline incremental memory hierarchy simulation. We extract symbolic information from the application executable and use this to generate detailed source-code correlated statistics including per-reference metrics, cache evictor information and stream metrics. Finally, we demonstrate how this information can be used to isolate and understand memory access inefficiencies. This illustrates a potential advantage of METRIC over compile-time analysis for sample codes, particularly when interprocedural analysis is required.

Categories and Subject Descriptors: D.3.4 [**Programming Languages**]: Processors—compilers; optimization; B.3.2 [**Memory Structures**]: Design Styles—cache memories

General Terms: Algorithms, Languages, Performance

Author's address: Jaydeep Marathe, Frank Mueller, Dept. of Computer Science, North Carolina State University, Raleigh, NC 27695-7534, mueller@cs.ncsu.edu, phone: (919) 515-7889.

Tushar Mohan, IBM India Research Lab, Block I, IIT, Hauz Khas, New Delhi 110016, India.

Sally A. McKee, School of ECE, Cornell University, Ithaca, NY 14853.

Bronis R. de Supinski, Andy Yoo, Lawrence Livermore National Lab, Center for Applied Scientific Computing, L-557, Livermore, CA 94551.

A preliminary version of this paper appeared in the International Symposium on Code Generation and Optimization, 2003 [Marathe et al. 2003]. This work was supported in part through the U.S. Department of Energy by the University of California, Lawrence Livermore National Laboratory under subcontracts: # B518219 and # B540203, NFS CAREER CCR-0237570, CNS-0406305, CCF-0429653 for Mueller; LLNL LDRD 01-ERD-043, NSF CCR-0073532 for McKee; and was performed in part under the auspices of the U. S. Department of Energy by University of California Lawrence Livermore National Laboratory under Contract W-7405-Eng-48, UCRL-JRNL-22545 for de Supinski and Yoo. This research was supported in part by the National Science Foundation through the San Diego Supercomputer Center under grant CCR-0237570 using the DataStar computing system. Mohan's contribution was in the course of his thesis at the University of Utah. This paper does not necessarily reflect or represent the views of IBM, Inc.

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

© 20YY ACM 0164-0925/20YY/0500-0001 \$5.00

Additional Key Words and Phrases: Dynamic binary rewriting, program instrumentation, data trace generation, data trace compression, cache analysis

#### 1. INTRODUCTION

Over the past decade, processor speeds have increased much faster than memory access speeds. Due to this trend, application execution times are increasingly dominated by the time spent in accessing memory. Tools are needed that can efficiently profile the memory access behavior of the program and help in detecting, isolating and understanding causes of the potential memory access inefficiencies. In this paper, we present one such tool, METRIC. METRIC employs incremental memory hierarchy simulation using partial memory access traces and generates detailed high-level metrics characterizing the application's memory use.

Simulation may be performed offline using previously extracted access traces or online as the application executes. In spite of the accuracy that trace-driven memory simulation affords, efficiency requirements dictate that it be used judiciously. For instance, software tracing incurs high runtime overheads, making full application simulation with reasonable data sets infeasible. Furthermore, even programs with short execution times may generate traces requiring gigabytes of storage. These limitations can be alleviated with partial data traces representing a subset of the access footprint of the target. Such traces tend to be comparatively small and less expensive to collect while still capturing the most critical data access points. Our focus is on scientific benchmarks, which generally employ algorithms with convergence criteria that are checked on a regular basis at the end of a timestep. The computation of each timestep is highly repetitive and, thus, representative for the overall application behavior, as shown elsewhere [Vetter and Mueller 2003]. Generating and exploiting partial data traces for online incremental memory hierarchy simulation addresses both high tracing overheads and large storage requirements without sacrificing accuracy. This is the approach we take.

METRIC stands for "MEmory TRacIng without re-Compiling". We draw on previous experience with partial data traces [Mueller et al. 2001] and binary rewriting [Marathe and Mueller 2002] to detect memory hierarchy bottlenecks. METRIC is also influenced by our work with large scale benchmarks [Vetter and Mueller 2003], another example of data centric computation where data sizes exceed cache capacities.

In this paper, we make the following contributions

- —We develop an approach that uses dynamic binary rewriting to extract memory access traces from executing applications.

- —We develop a novel algorithm for efficient access trace compression of programs with nested loop structures.

- —We present a cache analysis methodology (partially based on prior work by Mellor-Crummey et al. [Mellor-Crummey et al. 2001]) that uses partial access traces to generate cache metrics — including detailed evictor information — correlated to high-level constructs such as source code locations and data structures.

- -We show how METRIC can be used to understand a diverse range of memory access inefficiencies, some of which are hard to detect with static compiler analysis.

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

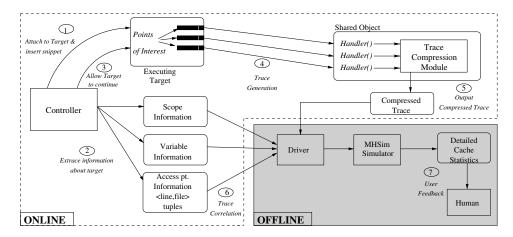

Fig. 1. The METRIC Framework

METRIC builds on the DynInst instrumentation framework [Buck and Hollingsworth 2000a] to exploit *dynamic binary rewriting*, or post link time manipulation of binary executables, enabling program transformation potentially even while the target is executing. Unlike conventional instrumentation, which generally requires compiler interaction (*e.g.*, for profiling) or inclusion of special libraries (*e.g.*, for heap monitoring), this approach obviates requirements of recompiling or relinking.

Dynamic binary rewriting can capture memory references of the entire application, including library routines, and it works equally well for mixed language applications commonly found in production scientific codes [Vetter and Mueller 2003]. The techniques can be adapted to address changing input dependencies and application modes, *i.e.*, changes over time in application behavior. Furthermore, binary manipulation techniques have been shown to offer new opportunities for program transformations, and these potentially yield performance gains beyond the scope of static code optimization without profile guided feedback [Bala et al. 2000].

#### 2. THE METRIC FRAMEWORK

The METRIC framework, shown in Figure 1, uses partial access traces for memory hierarchy simulation. Our framework extracts these comparatively small, low overhead access traces without compiler or linker support, *i.e.*, traces can be extracted from arbitrary executables. To achieve this, we dynamically modify the executing application by injecting instrumentation code via binary rewriting. We instrument memory access instructions to precisely capture the data access stream of the target application, and the user may activate or deactivate tracing so that data reference streams are selectively generated. This facility builds the foundation for capturing partial memory traces.

Figure 1 shows two phases in the process of analyzing bottlenecks with METRIC — *online* and *offline*. In the online phase, we instrument the application and extract the memory access trace. After trace generation is complete, the instrumentation is removed and the target application continues its execution without overhead. The traces are then used offline for memory hierarchy simulation in a background process or on a separate processor.

The flow of control is as follows. The user provides the application process id (PID) and

#### Jaydeep Marathe et al.

the names of the target function(s) to the controller program. The controller program attaches to the executing target and uses DynInst to access the Control Flow Graph (CFG) for these target functions. The text section of the target application is parsed and the *memory access* and *scope change* instructions are instrumented. Scope change instructions transfer control to enter or exit program scopes (such as functions and loop nests). Recording the scope change instructions allows the memory hierarchy simulator to aggregate the generated memory usage metrics at multiple levels of detail (scope) in the target application's source code. The instrumentation consists of calls to handler functions in a shared library. The shared library is loaded into the target's address space through a special one-shot instrumentation.

Once instrumentation is complete, the target is allowed to continue. As the instrumented application executes, different handler functions in the shared library get invoked, depending on the type of event being recorded, *i.e.*, load, store, enter\_scope and exit\_scope. The handler functions, in turn, call the compression routines, which attempt to detect regular patterns in the incoming stream. The compression routines maintain statistics about the regularity of the access stream seen at each memory access instruction. These metrics are presented to the user along with the memory access metrics generated by the memory simulator (in the next step).

After a specified number of events has been logged or a time threshold has been reached, instrumentation is removed, and the target continues executing without overhead. The compressed partial event trace is then used offline for incremental cache simulation. The cache simulator driver reverse maps addresses to variables in the source, using information extracted by the controller program, and it tags accesses to source code locations (source\_filename::line\_number). In addition to summary level information, the cache simulator generates detailed evictor information for source-related data structures. This information is presented to the user, along with the per-reference regularity metrics calculated by the compression algorithm.

For relating memory statistics to source code, we exploit source-related debugging information embedded in binaries. The application must provide the symbolic information in the binary (*e.g.*, generally by using the  $\neg g$  flag when compiling). Most modern compilers allow inclusion of symbolic information even if compiling with full optimizations. In particular, IBM's AIX and Intel/KAI compilers for the PowerPC do not suffer in their optimization levels when debugging information is retained. While some debugging information may suffer in accuracy due to certain optimizations, memory references are usually not affected. Thus, compiling with symbolic information only increases executable size without significant performance degradation.

### 3. TRACE GENERATION AND COMPRESSION

A large number of memory accesses can be generated within a short duration of monitoring, especially for memory-intensive codes. This access trace needs to be efficiently compressed before committing to stable storage. In addition, our compression algorithm maintains metrics describing the regularity of the access stream seen at each particular access point. These metrics provide key information during the analysis phase.

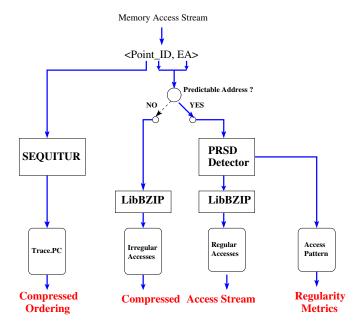

With this work we target scientific applications that tend to have highly regular accesses, usually in nested loops. We tailor our compression algorithm for this scenario. Our compression strategy is shown in Figure 2. The access stream to be compressed consists of

Fig. 2. Overall Compression Algorithm

individual records described by the tuple <point\_id, EA>. Point\_id denotes the access instruction and EA is the data address generated by the instruction. The task of compression is split into two parts. The ordering among the different access instructions is compressed separately from the data address generated by the individual access instructions. The idea is to use different compression algorithms suited to these distinct tasks to achieve more effective compression. It is necessary to record the access ordering for correct memory hierarchy simulation during the later phases.

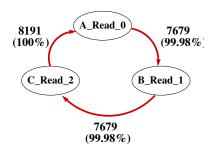

#### 3.1 Compressing Access Ordering

For applications with nested loops, the memory access instructions in the loop are executed in a very regular and predictable order. To exploit this regularity, we use the SEQUITUR compression algorithm to compress the IP/PC of such memory references. SEQUITUR is described by Nevill-Manning and Witten [Nevill-Manning and Witten 1997a], It converts a trace of symbols into a context-free grammar, and has time overhead linear in the number of symbols in the trace [Nevill-Manning and Witten 1997b]. The expansion of the grammar can be used to regenerate the original trace. SEQUITUR requires memory proportional to the total number of symbols occurring in the grammar. Since the total number of unique instruction addresses in the trace is usually small compared to the total program size, SEQUITUR is well suited for our purpose. We have observed extremely high compression rates with SEQUITUR on the SPEC2K FP benchmarks. In addition, decompression can proceed *incrementally*, *i.e.*, compressed traces can be used directly for cache simulation without an intermediate trace expansion step.

```

\begin{array}{c} RSD < access\_point, \, start\_address, \, length, \, address\_stride > \\ \{ & RSD\_1 < 1, \, \&A[0], \, N, \, 1 > \\ A[i] = B[2*i+2] + C[5*i]; \\ \} \\ RSD\_3 < 2, \, \&B[2], \, N, \, 2 > \\ RSD\_3 < 3, \, \&C[0], \, N, \, 5 > \\ \\ \hline Program \, Code \\ \hline \end{array}

```

Fig. 3. Example RSDs

#### 3.2 Compressing Trace Accesses

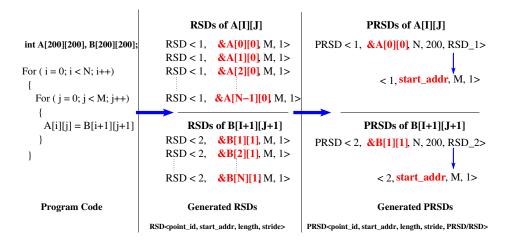

The accesses generated by each access point, i.e., the data addresses of memory references, are compressed separately. In other words, our compression scheme exploits the *local* value locality of each access point. The compression algorithm is tailored for regular accesses generated by tightly nested loops. The basic unit of representation for the compressed stream is the regular section descriptor (RSD), an extension of Havlak and Kennedy's RSDs [Havlak and Kennedy 1991]. Each RSD is a tuple <point\_id</pre>, start\_address, length, address\_stride>. Intuitively, each RSD compactly represents a stream of regular accesses generated at a given access point. The point\_id is the access point generating this RSD. The start\_address denotes the starting address of the stream, the length indicates the number of accesses in the RSD. The address\_stride denotes the change in addresses between successive addresses in the RSD. The stride of RSDs may be an arbitrary function. We restrict ourselves to constants in this paper since we require fast online techniques to recognize RSDs. In different contexts, one may want to consider linear functions or higher order polynomials. Recurring references to a scalar or to the same array element map to RSDs with a constant address stride of zero. An example RSD is shown in Figure 3, assuming each array element has size one.

RSDs are only sufficient to describe accesses generated by a single innermost loop. In order to efficiently describe accesses by a *nest* of loops, we introduce the *power* regular section descriptor (PRSD). A PRSD is described by the tuple *<point\_id*, *start\_address*, *length*, *address\_stride*, *child\_RSD>*. A PRSD is similar to an RSD, but instead of generating *addresses*, it generates instances of PRSDs or RSDs. The address\_stride of the PRSD represents the difference in addresses between the starting addresses of two consecutive child PRSD/RSDs. Thus the recursive structures of the PRSD allows efficient representation of regular accesses generated in tight loop nests.

An example PRSD is shown in Figure 4, assuming the size of integers is one and arrays are laid out in row major order. The RSDs for the A[i][j] and B[i+1][j+1] access points are calculated separately. There are N RSDs for each access point, each corresponding to one iteration of the outer i loop. These RSDs are compactly represented by the PRSDs shown on the right side. For example, consider the PRSD for access point of A[i][j]. The PRSD has length N, the length of the outer loop. The address stride of the PRSD is 200, since the starting addresses of A[i][j] in consecutive iterations of the i loop differ by 200.

Each instance of the PRSD is an RSD that has M elements and an address stride of one. This RSD describes all iterations in the inner j loop. The compression of data accesses proceeds as follows. The PRSD detector checks whether the incoming data access is pre-

Fig. 4. Example PRSDs

dictable by a PRSD/RSD. If the access is predictable, the PRSD/RSD data structures are updated. Accesses may cause evictions of currently existing PRSDs/RSDs (as described in the next section). These evicted PRSDs/RSDs are further compressed by a second stage compressor based on the open source BZIP2 package [Seward 2005]. BZIP2 compresses using a block sorting algorithm described by Burrows and Wheeler [Burrows and Wheeler 1994].

RSDs with less than three elements are considered irregular accesses. Irregular accesses are compressed by a separate instance of the BZIP2-based second stage compressor. In addition to compression, the PRSD detector also computes metrics characterizing the regularity of the data accesses generated by each access point. These metrics are presented in later sections and help in deeper understanding of the program's memory access behavior.

#### 4. ONLINE DETECTION OF PRSDS AND RSDS

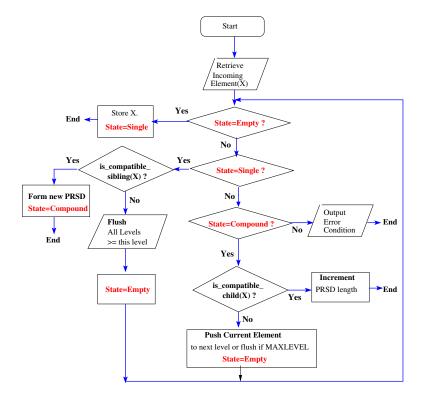

In this section we introduce our algorithm for efficient detection of PRSDs and RSDs from the data access stream generated at each access point. To simplify the notation, we consider RSDs to be a special instance of PRSDs in the description of the algorithm. The *height* of the PRSD denotes the number of child RSDs encapsulated by the PRSD, and indicates the degree of hierarchy of the PRSD. RSDs have height zero (since they themselves do not have child RSDs).

The algorithm is intuitive. The algorithm builds up hierarchical structures (*i.e.*, PRSDs) as data accesses are generated at the access point. If a PRSD exists for the access point, and it can predict the incoming data access, then the PRSD length is simply incremented, and processing ends. Changes in the access stream (*e.g.*, the beginning of a new loop iteration) can cause the current PRSD to fail to predict the incoming access. This triggers formation of a new PRSD, and potentially *flushes* the current PRSD to the output buffer.

#### 4.1 Levels

For each access point, we maintain a list of numbered *levels*. Each level contains a single PRSD. Higher-numbered levels contain more deeply nested PRSDs, *i.e.*, PRSDs with in-

Fig. 5. PRSD Detector Flowchart: Processing in a Level

creasing heights. The current data access to be compressed is processed at the lowest level, i.e., level zero. This may trigger the movement of any existing RSD at level zero to the next level, which may trigger the upward movement of PRSDs to higher-numbered levels.

Each level is always in one of three states — *empty*, *single* or *compound*. A level in state empty has no PRSDs. Similarly, a level in state single has only a single PRSD. A level in state *compound* has a composite PRSD. The idea is that an incoming PRSD at this level would be checked against the composite PRSD to see if it qualifies as a "child" of the composite PRSD. If so, we only need to increment the length of the composite PRSD by one — the incoming PRSD was expected. For streams with long regular accesses, we expect the level to be in the *compound* state for long stretches of processing.

#### Per-level Processing

Figure 5 shows the processing at each level. All levels are initially empty. Let X denote the incoming element to be processed at the current level number. As described earlier, the data access to be compressed is processed at level zero. Thus, X for level zero will be simply a data address. At higher-numbered levels, X will be a PRSD.

The processing of X is determined by the current state of the level. If the level is *empty*, the incoming element is simply stored, the level state is changed to single and processing ends.

If the level is in state *single*, there already exists a PRSD "Y" at this level. We try ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

to combine the incoming element X with the current element Y to form a more deeply nested PRSD with a height equal to the height of Y plus one. This checking is done by the function <code>is\_compatible\_sibling</code>. Two PRSDs are compatible if they have the same height, length and their children are also compatible with each other (checked recursively by <code>is\_compatible\_sibling</code>). If the elements are compatible, a new PRSD ("composite PRSD") is formed with length two and a height equal to the height of Y plus one. This new PRSD will have the start\_address same as the start\_address of Y and an address\_stride of the difference between the start\_addresses of Y and X, and it will encapsulate Y as the child\_prsd.

If X and Y are not compatible siblings, a change in the data access pattern is detected, *e.g.*, caused by a phase change in the program. We then flush all PRSDs in the current and higher-numbered levels, reset the level state to *empty* and resume processing. In this manner, phase changes are gracefully detected and handled.

Finally, the level might be in the *compound* state, indicating the presence of a composite PRSD "Y". If so, we check if the incoming element X can be considered a child of this PRSD. This check is performed by the <code>is\_compatible\_child</code> function. The function first checks if X is a compatible sibling of the *children* of Y, using the <code>is\_compatible\_sibling</code> function introduced before. Next, the function checks if the start\_address of X is equal to Y.start\_address + Y.length \* Y.address\_stride, *i.e.*, if X is the next instance of the PRSDs produced by Y. If <code>is\_compatible\_child</code> succeeds, we simply increment the length of Y and processing ends.

If X is not a compatible child of Y, we push Y to the next level (where it is processed according to the flowchart), reset the level state to *empty*, and restart processing at this level with X again. The idea is that with future accesses, X might form a new PRSD Z that is compatible with Y. Z will be compared to Y when Z is pushed to the next level (If this new PRSD Z is still incompatible with Y, the flowchart illustrates that this will cause Y to be flushed). With access points in a recursive function, the number of levels is potentially unbounded. To guard against this, we specify a MAXLEVEL constant value beyond which the element being pushed is simply flushed to the output buffer, rather than being re-processed at a higher level.

#### 4.3 Example

Figure 6 shows the operation of the PRSD detection algorithm for the A[i][j] reference shown in Figure 4. The figure shows the accesses generated at different instances of the loop nest, the expected actions that the algorithm executes, and the state of the data structures after these actions.

Let us step through some of the frames in the example. For each frame, we show the value of the loop index variables i and j and the corresponding memory address generated, which is input to the PRSD detection algorithm.

**Frame 1**: This shows the initial state. All the levels are in state *empty*.

**Frame 2**: (i=0, j=0, &A[0][0]): This is the first iteration point in the loop nest. The incoming element is stored in level zero and the state of the level is changed to *single*.

**Frame 3**: (i=0, j=1, &A[0][1]): The incoming element and the resident element are compared to verify that they can be combined into a composite PRSD (is\_compatible\_sibling). The new composite PRSD has length two, and the state of the level is updated to *compound*.

Frame 4: (i=0, j=2, &A[0][2]): The incoming element is checked to verify

$ACM\ Transactions\ on\ Programming\ Languages\ and\ Systems,\ Vol.\ V,\ No.\ N,\ Month\ 20 YY.$

| Input: (liter, Jiter), address                                | 1 Input: None (initial State)                               | 2 Input: (i=0,j=0) &A[0][0]                                      |

|---------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|

| Action: What steps to take for this input element.            | Action: None. All levels are empty.                         | Action: Store element in level-0. Update level-0 state           |

| int A[200][200]                                               | Level 0. State= Empty                                       | Level 0. State= Single                                           |

| For $(i=0; i < N; i++)$                                       |                                                             | < &A[0][0] >                                                     |

| { For( $j=0$ ; $j < M; j++$ )                                 |                                                             |                                                                  |

| {                                                             | Level 1. State= Empty                                       | Level 1. State= Empty                                            |

| A[i][j] =<br>}                                                |                                                             |                                                                  |

| }                                                             |                                                             |                                                                  |

| 3 Input: (i=0,j=1) &A[0][1]                                   | 4 Input: (i=0,j=2) &A[0][2]                                 | 5 Input: (i=0,j=N-1) &A[0][M-1]                                  |

| Action: is_compatible_sibling? YES Form composite PRSD.       | Action: is_compatible_child ? YES Increment PRSD length.    | Action: is_compatible_child ? YES Increment PRSD length.         |

| Land O State Communi                                          | Level 0 State Common d                                      | Laurin State Communi                                             |

| Level 0. State= Compound                                      | Level 0. State= Compound                                    | Level 0. State= Compound                                         |

| RSD: < Start_addr= &A[0][0],<br>Addr_stride = 1               | RSD: < Start_addr= &A[0][0],<br>Addr_stride = 1             | RSD: < Start_addr= &A[0][0],<br>Addr_stride = 1                  |

| Length = 2 >                                                  | Length = 3 >                                                | Length = M >                                                     |

| Level 1. State= Empty                                         | Level 1. State= Empty                                       | Level 1. State= Empty                                            |

| 6 Input: (i=1,j=0) &A[1][0]                                   | 7 Input: (i=1,j=1) &A[1][1]                                 | 8 Input: (i=1,j=M-1) &A[1][M-1]                                  |

| Action: is_compatible_child ? NO !                            | Action:                                                     | Action:                                                          |

| Push PRSD to level-1.                                         | Level-0: is_compatible_sibling? YES                         | is_compatible_child ? YES                                        |

| Re-process incoming element  Level 0. State= Single           | Form composite PRSD.  Level 0. State= Compound              | Increment PRSD length.  Level 0. State= Compound                 |

| < &A[1][0] >                                                  | RSD: < Start_addr= &A[1][0],  Addr_stride = 1  Length = 2 > | RSD: < &A[1][0], 1, M>                                           |

| Level 1. State= Single<br>RSD: < &A[0][0], 1, M-1>            | Level 1. State= Single<br>RSD: < &A[0][0], 1, M-1>          | Level 1. State= Single<br>RSD: < &A[0][0], 1, M>                 |

| 9 Input: (i=2,j=0) &A[2][0]                                   | (10) Input: (i=3,j=0) &A[3][0]                              | 11) Input: (i=N-1,j=M-1) &A[N-1][M-1]                            |

| Action:                                                       | Action:                                                     | Action:                                                          |

| 1. Push RSD to level-1 2. Level-1: is_compatible_sibling? YES | 1. Push RSD to level-1 2. Level-1: is_compatible_child? YES | Level-0: is_compatible_child ? YES                               |

| 3. Level-1: Form composite PRSD                               | 3. Level-1: increment PRSD length                           | This is how data structures look after last access in loop nest. |

| 4. Level-0: re-process incoming element                       | 4. Level-0: re-process incoming element                     |                                                                  |

| Level 0. State= Single<br>< &A[2][0] >                        | Level 0. State= Single < &A[3][0] >                         | Level 0. State= Compound<br>RSD: < &A[N-1][0], 1, M>             |

| Level 1. State= Compound                                      | Level 1. State= Compound                                    | Level 1. State= Compound                                         |

| PRSD:<<br>Start_addr= &A[0][0]                                | PRSD:<<br>Start_addr= &A[0][0]                              | PRSD:<<br>Start_addr= &A[0][0]                                   |

| Addr_stride = 200, Length = 2,                                | Addr_stride = 200,                                          | Addr_stride = 200, Length = N-1,                                 |

| Child_RSD=<-,stride=1,length=M>                               | Child_RSD=<-,stride=1,length=M>                             | Child_RSD=<-,stride=1,length=M>                                  |

Fig. 6. PRSD Detection Example

that it can be considered to be a *child* of the currently resident composite PRSD (is\_compatible\_child). The length of the composite PRSD is incremented by one and processing ends.

Now we skip to the last iteration of the i loop in the same iteration of the i loop.

**Frame 5**: (i=0, j=M-1, &A[0][M-1]): The incoming element qualifies as a child of the resident PRSD (is\_compatible\_child). The length of the resident PRSD is incremented by one and processing ends.

**Frame 6**: (i=1, j=0, &A[1][0]): This is the very next iteration point of the loop nest after Frame 5 and is the first access in iteration 1 of the i loop. Assuming M is smaller than 200 (the lower dimension of the array), the currently resident PRSD will not correctly predict the incoming element (the PRSD will predict address &A[0][M+1], the incoming address is &A[1][0]), i.e., is\_compatible\_child will fail. The currently resident PRSD is pushed to the next level, and the incoming element is saved in the current level.

**Frame 9**: (i=2, j=0, &A[2][0]): This is the next iteration point after Frame 8. The incoming element will not be predicted by the currently resident PRSD on level zero (similar to Frame 6), which will cause the PRSD to be pushed to the next level (level one). In level one, this PRSD is compared to the pre-resident PRSD to verify that they are compatible siblings ( $is\_compatible\_sibling$ ), after which a new composite PRSD is formed with length two, as shown. The state of level zero is reset to *empty* and processing is restarted with the incoming address &A[2][0].

**Frame 10**: (i=3, j=0, &A[3][0]): Similar to Frame 9, the resident PRSD at level zero will not be able to predict the incoming address &A[3][0]. This will cause the resident PRSD to be pushed upwards to level one, where it will qualify as a child of the pre-resident PRSD. This will cause the length of the pre-resident PRSD at level one to be incremented by one, as shown.

**Frame 11**: (i=N-1, j=M-1, &A[N-1][M-1]): This is the last access of the loop nests. The incoming element will be correctly predicted by the currently resident PRSD in level zero (similar to Frame 5). The state of the data structures at the end of this access is as shown — there is an RSD at level zero and a PRSD at level one. Future accesses at the current access point will cause the RSD to be pushed to level one where it will qualify as a child of the pre-resident PRSD.

#### 4.4 Space Complexity

In the worst case, a completely random sequence of addresses can be passed to the PRSD detection algorithm. In this case, no RSDs or PRSDs will be detected and the accesses will be recorded individually as irregular accesses. Thus, the space complexity of the algorithm is O(M), where *M* is the total number of accesses (*i.e.*, linear space complexity). The best case input is a stream of regular accesses. For such input the algorithm would, at best, generate exactly one PRSD for each access point. The space required to represent a PRSD is proportional to its *height*. The height of the PRSD in a particular level can be at most one greater than the level number, which has an upper bound given by the constant value MAXLEVELS. Thus, the space complexity to represent the PRSDs for n access points is bounded as O((MAXLEVELS+1)\*n). n is an attribute of the source code and is constant for the duration of monitoring. Since both factors are constant, the best case space complexity has a constant upper bound.

#### 4.5 Time Complexity

Since we must look at each incoming element to compress it, the lower bound on the time complexity is given as  $\Omega(M)$ , where M is the total number of accesses in the trace. A particular incoming access may trigger movement of PRSDs/RSDs to highernumbered levels, where they need to be re-processed. The number of re-processing steps is bounded by the maximum number of levels (MAXLEVELS) and the height of the PRSD, which can be at most (MAXLEVELS+1). Thus, the upper bound on time complexity is O(M\*MAXLEVELS\*MAXLEVELS). Since MAXLEVELS is constant, the upper bound on the time complexity is linear in the number of accesses in the trace.

#### **EVALUATION OF THE COMPRESSION SCHEME**

In this section, we evaluate the performance of our compression scheme with respect to compression efficiency and time required for compression. We compare our results for 12 out of the 14 SPEC2000FP benchmarks <sup>1</sup>. Results are compared against VPC3, a stateof-the-art compression algorithm based on using value predictors for data compression [Burtscher 2004a].

#### 5.1 VPC3

VPC3 is targeted for compression of extended address traces. Such traces contain the instruction address (PC) of the access instruction, followed by one or more register values or effective addresses (EA). VPC3 first splits the access stream into separate streams of PCs and EAs. The algorithm has a bank of value predictors that attempt to predict the target element value (PC or EA). All predictors are updated after each element has been processed. VPC3 by itself does not compress the trace. Instead, it writes out the id of the value predictor that successfully predicted the current element. This stream of ids is compressed by a second stage compressor based on BZIP2. Elements that were not predicted by any predictor are compressed by a separate instance of the second stage compressor. In our experiments, we use the VPC3 source code obtained from the author's website [Burtscher 2004b] and couple the output to a second stage compressor based on BZIP2 [Seward 2005].

We use VPC3 for comparison since it represents the state-of-the-art in compressing access traces. VPC3 has been shown to compress faster and with more effective compression rate for most benchmarks, compared to several contemporary compression algorithms (SEQUITUR, BZIP2, GZIP) [Burtscher 2004a]. VPC3 is targeted towards efficiently compressing the address traces of general purpose programs while we focus specifically on programs found in scientific computing. However, in addition to compressing access traces, our approach generates metrics that *characterize* the address stream (described later in Section 9). These metrics, along with the results generated by the simulator, provide insight into the application's memory access behavior.

#### 5.2 Experimental Setup

For our compression scheme we used the open source implementation of SEQUITUR [Manning 2005]. All benchmarks were compiled at -O2 optimization level on an IBM POWER4 platform. All benchmarks used "training" data sets. The static call graph of

$<sup>^1</sup>$ 191.fma $^3$ d failed to run because DynInst ran out of memory for instrumentation code.  $^3$ 01.apsi failed due to an internal error in DynInst.

| Benchmark      | Our Algorithm | VPC3      | Ratio: (Ours) / VPC3 |

|----------------|---------------|-----------|----------------------|

| 171.swim       | 910608.59     | 154698.98 | 5.886                |

| 168.wupwise    | 144.74        | 221.48    | 0.653                |

| 172.mgrid      | 70847.45      | 4765.63   | 14.866               |

| 173.applu      | 337.52        | 133.94    | 2.519                |

| 177.mesa       | 1519.42       | 6183.17   | 0.245                |

| 178.galgel     | 1938.03       | 4466.73   | 0.433                |

| 179.art        | 283312.87     | 40380.65  | 7.016                |

| 183.equake     | 12.23         | 99.55     | 0.122                |

| 187.facerec    | 2382.55       | 618.93    | 3.849                |

| 188.ammp       | 1496.68       | 1152.85   | 1.298                |

| 189.lucas      | 607.34        | 437.52    | 1.388                |

| 200.sixtrack   | 181.24        | 488.11    | 0.371                |

| Geometric_Mean | 2196.76       | 1636.89   |                      |

| Harmonic_Mean  | 118.76        | 407.20    |                      |

| Average        | 106115.72     | 17803.97  |                      |

Table I. Comparison of Compression Rates

the target program was traversed with main as root, and all memory access points in the call graph were instrumented. Up to one billion  $(10^9)$  accesses were traced and compressed online for each benchmark. All benchmarks reached the one billion limit, except for 177.mesa  $(8x10^6 \text{ total accesses})$  and 188.ammp  $(531x10^6 \text{ total accesses})$ .

#### 5.3 Comparison of Compression Rates

The compression rate was computed as follows. The uncompressed access trace is composed of <point\_id, address> records. Each uncompressed record requires six bytes — four bytes for the 32-bit address and two bytes for the point\_id. Notice that all our programs had less than 65536 memory access points. Thus the total uncompressed trace size is (# total\_records) \* 6. The compression rate is calculated as  $\frac{size\ of\ un-compressed\ trace}{size\ of\ compressed\ trace}.$

Table I shows the compression rate for our algorithm and for VPC3. The last column shows the relative compression rate of our algorithm compared to VPC3. The table shows that both VPC3 and our algorithm achieve substantial compression rates on almost all the benchmarks. For 7 out of the 12 benchmarks, our algorithm achieves a better compression rate than VPC3 (boldface ratio in last column greater than one). For some programs with very regular loop nest oriented structures, our algorithm achieves spectacularly large compression rates (swim, mgrid, art), due to our use of hierarchical PRSD structures. Overall, the geometric mean of the compression rate of our algorithm is about 25% greater than the value for VPC3.

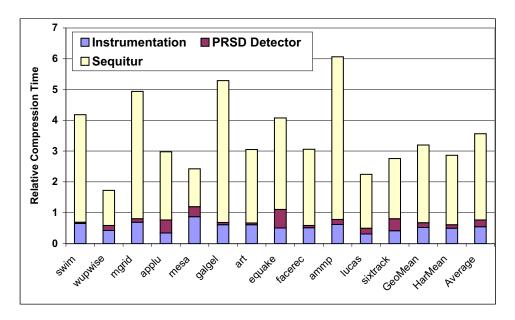

#### 5.4 Comparison of Compression Times

Figure 7 shows the time required for compression using our algorithm. The time for three different components is shown. *Instrumentation* denotes the overhead of the binary instrumentation framework (*e.g.*, saving/restoring register context). *PRSD Detector* denotes the overhead of the PRSD detection algorithm introduced in the last section. *Sequitur* denotes the overhead of the SEQUITUR-based compression of the trace ordering. The values are relative to the time taken by the VPC3-based online compression framework (including

Fig. 7. Execution Time Breakup for Our Compression Scheme, Relative to VPC3 Execution Time

instrumentation overhead, which should be similar in both cases). Our algorithm is on average three times slower than the VPC3 implementation. By far the most expensive component is the SEQUITUR-based module for compressing the trace ordering. It may be possible to reduce this overhead by using a more optimized version of SEQUITUR. Alternately, we could update the stride predictor in VPC3 to use PRSDs. This modified VPC3 would be much faster than our current approach while allowing us to leverage VPC3's compression capabilities on programs where the accesses are less regular. However, we would lose structural information inherent to PRSDs after BZIP compression. Nevertheless, the PRSD predictor would still generate the *regularity* metrics (discussed later in Section 9) that complement the results generated by the memory hierarchy simulator. Finally, we note that METRIC is capable of and intended for gathering *partial* access traces, where the overhead of trace compression is limited by the duration of monitoring. Thus, in practice, a slightly more expensive scheme might still be acceptable as long as the trace collection period is short.

#### 6. MEMORY HIERARCHY SIMULATION

The compressed trace obtained in the preceding sections is used offline for incremental memory hierarchy simulation. After a partial trace of accesses has been collected, the instrumentation is removed dynamically and the application continues execution without overhead. For programs that exhibit distinct phases of execution (*e.g.*, time-stepped programs), this allows us to limit the overhead of performance analysis by capturing and simulating only "snippets" of the complete trace.

For memory hierarchy simulation, we use a modified version of MHSim [Mellor-Crummey et al. 2001]. MHSim simulates the data TLB (translation Lookaside Buffer) and multiple levels of cache. MHSim maintains information *per-reference*, allowing "bulk

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

metrics" regarding memory performance (*e.g.*, hits, misses) to be drilled down and mapped to individual access points. For each access point, it generates a rich set of metrics that we shall discuss further below. The original MHSim package used a source-to-source Fortran translator to annotate data accesses with calls to MHSim cache simulation routines. This strategy has two significant disadvantages, which we overcome with our approach.

The most serious problem with source instrumentation is that it may significantly distort the actual memory access behavior of the program without instrumentation. Annotating the source code accesses with function calls to MHSim routines will potentially inhibit many important and well established loop reordering transformations (e.g., loop interchange, tiling), because of the additional true dependences introduced by the function calls. It may also prevent or modify other standard compiler optimizations, such as common sub-expression elimination (due to presence of function calls accepting addresses of array references). Thus, the resultant executable with instrumentation can be totally different (in terms of memory access patterns) from the original uninstrumented version — which can lead to potentially misleading diagnostic information reported by MHSim. In contrast, by instrumenting the final optimized binary generated by the compiler, we guarantee that we still capture the exact original access pattern. Thus, we can generate diagnostic information that correctly reflects the target program behavior. Consequently, we argue that source-level instrumentation is the wrong abstraction level for capturing the original application behavior and can lead to potentially misleading results for programs in our target domain (loop-oriented scientific codes).

The second major problem with source-level instrumentation frameworks is that they are limited to a particular language. Many scientific programs are mixed-language applications [Vetter and Mueller 2003]. In addition, many programs make heavy use of libraries (e.g., Standard C library (libc), math and numerical libraries, networking libraries), that a source level instrumentation frameworks will be unable to instrument. Thus the resultant trace of memory accesses may be incomplete and can lead to potentially misleading diagnostic information. In contrast, our approach is independent of any language, compiler and linker. More importantly, we use *dynamic* binary rewriting that allows us to instrument target applications as they are executing. Thus, we can turn the instrumentation on and off, enabling the capture of *partial* access traces as discussed before. The resulting overhead of trace collection and instrumentation is flexible and is only limited to the duration of monitoring.

#### ABSTRACTING TRACE DATA

The compressed trace contains "raw" instruction addresses (point\_ids) and data addresses. We use the symbolic information embedded in the binary to map the instruction addresses to source code locations (filename::line\_number). We also try to reverse map the raw data address to a symbolic variable name using information extracted from the embedded symbol table. Global variable names and sizes are easily obtained from the symbol table. We also support local variables by keeping records of function entry and exit in the trace, and by recording the value of the stack pointer on entry. The symbol table for local variables only contains the address *offsets* in the current activation record of the function. Combined with the value of the stack pointer recorded in the trace, this allows us to reverse map accesses to function-local variables. Finally, dynamically allocated variables can be partially supported by instrumenting the entry to allocation functions (malloc/calloc/free) and walk-

ing the call stack at allocation to create a unique "allocation context" identifier. The data accesses to elements in the dynamically allocated area will be reverse mapped and tagged to this identifier in the MHSim report.

#### MHSIM-GENERATED METRICS

MHSim generates metrics for each level of cache and also for the data TLB. Metrics can be aggregated by reference, by variable and by loop nest. We shall list and describe each metric and later discuss their value as diagnostic input to understand memory behavior. MHSim generates the following metrics per-reference:

- —**Hits**: Number of accesses by this reference point that hit in the cache.

- —Misses: Number of accesses by this reference point that missed in the cache.

- —Miss Ratio Ratio of hits to misses.

- —**Temporal Hit Fraction**: The fraction of the hits that occurred due to *temporal reuse* of data. Calculated as  $\frac{temporal\ hits}{total\ hits}$ . MHSim uses bit vectors to maintain information about which byte offsets in the cache line were addressed by access instructions, allowing classification of hits into temporal and non-temporal hits. Temporal hits include hits caused by both *self-reuse* (same reference point accesses a memory location multiple times) and *cross-reuse* (different reference points access same memory location).

- —**Spatial Hit Fraction**: This is defined as 1 temporal\_hit\_fraction, *i.e.*, non-temporal hits are classified as purely spatial hits.

- —**Spatial Reuse**: This value gives the average fraction of the memory line in bytes that was *used*, *i.e.*, explicitly addressed by a memory access instruction, before the memory line was evicted from the cache. It is computed as  $\frac{used\ bytes}{cache\ line\ size*number\ of\ evictions}.$

- —Evictor References: For each reference, MHSim maintains a list of evictor references that evicted this reference from the cache. Evictors provide insight into cache conflicts. Cycles of evictors potentially indicate conflict misses which could be removed by transformations like padding.

#### 9. STREAM-ORIENTED METRICS

In addition to the metrics generated by MHSim, the PRSD detector in the compression algorithm also generates complementary metrics characterizing the regularity of the access stream. These metrics are calculated separately for each access point. The following metrics are generated:

- —**Regularity ratio**: Computed as total predictable accesses to those detected as an instance of an RSD or PRSD. The regularity ratio allows us to classify access points into irregular and regular categories. Access points with high regularity ratios can be targeted for stream-based optimizations, as described in our previous work [Mohan et al. 2003]. For example, the predictable nature of the access point can be exploited by prefetching, which caches future data access early to lessen effective access latencies.

- —**Mean stream length**: The average of the length of all RSDs generated at this point.

- **—# Distinct lengths**: Number of distinct RSD lengths seen at this access point.

- —% **Distribution of distinct lengths**: The distribution of RSDs according to their lengths.

- **—# Distinct strides**: Number of address strides for all RSDs seen at this point.

—% Distribution of distinct strides: The distribution of RSDs according to their address strides.

The definition of regularity ratio as defined here differs from the definition in our previous work [Mohan et al. 2003]. In our previous work, the regularity ratio was a single value calculated over the *entire* program or program section to characterize the stream behavior. Access streams were not segregated by access point, *i.e.*, a stream could contain accesses from different access points. In contrast, in this work we segregate the access stream by access points and calculate the regularity metrics for each point separately. Thus, we can now obtain a much finer level of information tagged to individual access points, instead of a single aggregate value for the whole program or program section.

#### DIAGNOSIS OF PERFORMANCE PROBLEMS

In previous paragraphs, we introduced several metrics to quantify different facets of memory access performance. What diagnostic information do these metrics provide? How can we use them to understand the symptoms and the underlying causes of memory access inefficiencies? Figure 8 gives a short overview of how the generated metrics can be used for this task.

METRIC gives insight on the memory access patterns of the target program. The information provided by METRIC allows the program analyst to focus on the bottleneck of the program, and also gives indications on how a bottleneck can be removed by manually applying program or data transformations. Many of these transformations can also be achieved by contemporary compiler technology. Such transformations were presented in our earlier work for some well known computation kernels [Marathe et al. 2003]. This paper will not reiterate them. Instead, we shall use METRIC to optimize several sample codes to illustrate its potential advantage over compile-time analysis, particularly when interprocedural analysis is required. For clarity of presentation, the sample codes are microbenchmarks that manifest a particular performance weakness. They represent behavior that can arise in larger real world programs.

## 10.1 Use case: Cache Reuse Hinting

Consider the following snippet of C code:

```

1

double A[MATDIM], B[MATDIM];

double C[MAT2], D[MAT2];

3

4

void do_sum()

5

6

for(i=0;i < MATDIM;i++)</pre>

7

A[i] = A[i] + B[i];

8

9

10 void do_mult(void)

11

{

12

for(j=0; j < 1500; j++)

C[ind[j]] *= D[ind[j]];

13

14

}

15

void main()

```

| Metric           | Diagnostic Information                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Miss Ratio       | A basic measure of performance. References with high or medium                                                                             |

|                  | miss ratios should be specifically singled out for further analysis.                                                                       |

|                  | A high miss ratio, when other indicators like regularity ratio and                                                                         |

|                  | stream lengths have favorable values, indicates presence of specific                                                                       |

|                  | cache access inefficiencies.                                                                                                               |

| Temporal Hit     | This measures how much temporal reuse is being realized for the                                                                            |

| Fraction         | memory lines accessed by this reference. Low value may indicate                                                                            |

|                  | that the reference is being flushed from cache before reuse could                                                                          |

|                  | occur. If low temporal reuse is inherent to the reference, <i>cache hint</i> -                                                             |

|                  | ing can be used to avoid allocating a cache line (this requires other                                                                      |

|                  | indicators to show specific behavior, see text for use case).                                                                              |

| Spatial Reuse    | Low values indicate that cache is not being used efficiently — data                                                                        |

|                  | is being brought in which is never "touched" before the memory line                                                                        |

|                  | is evicted from cache. Can indicate presence of conflict misses, if                                                                        |

|                  | regularity metrics (regularity ratio, stride values) show regular and                                                                      |

|                  | low-strided access behavior.                                                                                                               |

| Evictor Refer-   | A cycle of evictors coupled with other indicators like low spatial                                                                         |

| ences            | reuse can indicate presence of conflict misses. The advantage of                                                                           |

|                  | evictor references is that it tells us <i>precisely</i> which references are                                                               |

|                  | involved in the conflict, allowing straightforward code/data trans-                                                                        |

|                  | formations to correct it. On the other hand, when other indicators of                                                                      |

|                  | cache efficiency (e.g., spatial reuse) are high, cycles of evictors may                                                                    |

|                  | still indicate the presence of <i>capacity</i> misses — there is simply not                                                                |

|                  | enough room in the cache to keep all the accessed data at the same                                                                         |

| Regularity ratio | time.                                                                                                                                      |

| Regularity ratio | Highly regular streams produce <i>predictable</i> values, which can be exploited by optimizations like prefetching. On the other hand, ir- |

|                  | regular references can be optimized by another class of optimiza-                                                                          |

|                  | tions (e.g., cache hinting). References with high regularity ratios                                                                        |

|                  | that still have high miss rates reveal the presence of cache access                                                                        |

|                  | inefficiencies.                                                                                                                            |

| Mean stream      | Optimizations like prefetching require a minimum stream length to                                                                          |

| length           | be profitable.                                                                                                                             |

| % Distribution   | Low-strided references should be expected to have high spatial reuse                                                                       |

| of strides       | values, otherwise a cache access inefficiency is indicated. If there                                                                       |

| 01 3011003       | are only a few dominant strides, it may simplify the implementation                                                                        |

|                  | of optimizations like prefetching (knowing dominant stride value                                                                           |

|                  | allows manual insertion of prefetch instructions without depending                                                                         |

|                  | on the compiler.)                                                                                                                          |

|                  | p··/                                                                                                                                       |

Fig. 8. Use of Metrics for Performance Diagnosis

```

17 {

18     for(i=0;i < timesteps;i++)

19     {

20          do_sum();

21          do_mult();

22     }

23 }</pre>

```

There are four distinct arrays A, B, C and D in the first use case. The functions do\_sum() and do\_mult() are called once per timestep. This program was compiled and traced under our framework on a Power4 platform using the IBM xlc compiler A cache with the following parameters was simulated: cache size=256 KB, associativity=8, line size=128, writeback cache, LRU replacement policy. This configuration is similar to the L2 cache of the Itanium2 processor [Intel 2004]. The per-reference results generated by the simulator are shown in Figure 9. Figure 9(a) shows the cache metrics generated by the simulator, and Figure 9(b) shows the stream metrics generated by the PRSD detector.

10.1.1 Analysis. The reference name shown in the results has the following syntax: VariableName\_Accesstype\_id. VariableName is the symbolic identifier that corresponds to the memory address being accessed. Accesstype can be either Read or Write. Finally, id

|         |      |                 |            |        |        | Miss  | Temporal | Spatial |

|---------|------|-----------------|------------|--------|--------|-------|----------|---------|

| File    | Line | Reference       | Source Ref | Hits   | Misses | Ratio | Ratio    | Reuse   |

| reuse.c | 13   | D_Read_12       | D[ind[i]]  | 1532   | 13468  | 0.897 | 0.1566   | 0.0639  |

| reuse.c | 13   | C_Read_11       | C[ind[i]]  | 1929   | 13071  | 0.871 | 0.320    | 0.0639  |

| reuse.c | 7    | A_Read_7        | A[i]       | 96125  | 6275   | 0.061 | 0.021    | 0.9867  |

| reuse.c | 7    | B_Read_8        | B[i]       | 96135  | 6265   | 0.061 | 0.023    | 0.9860  |

| reuse.c | 13   | $ind\_Read\_10$ | ind[i]     | 14530  | 470    | 0.031 | 0.019    | 0.9134  |

| reuse.c | 13   | C_Write_13      | C[ind[i]]  | 15000  | 0      | 0.0   | 1.0      | 1.0     |

| reuse.c | 7    | A_Write_9       | A[i]       | 102400 | 0      | 0.0   | 1.0      | 1.0     |

(a) Per-Reference Cache Statistics

|             | Total    | Predictable | Regularity | Average | # Distinct | % Stride      |

|-------------|----------|-------------|------------|---------|------------|---------------|

| Reference   | Accesses | Accesses    | Ratio      | Length  | Strides    | Distribution  |

| D_Read_12   | 15000    | 0           | 0.0        | 0       | 0          | -             |

| C_Read_11   | 15000    | 0           | 0.0        | 0       | 0          | -             |

| A_Read_7    | 102400   | 102400      | 1.0        | 10240   | 1          | stride=8,100% |

| B_Read_8    | 102400   | 102400      | 1.0        | 10240   | 1          | stride=8,100% |

| ind_Read_10 | 15000    | 15000       | 1.0        | 1500    | 1          | stride=4,100% |

| C_Write_13  | 15000    | 0           | 0.0        | 0       | 0          | -             |

| A_Write_9   | 102400   | 102400      | 1.0        | 10240   | 1          | stride=8,100% |

(b) Per-Reference Stream Statistics

Fig. 9. Original Per-Reference Memory Usage Statistics

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

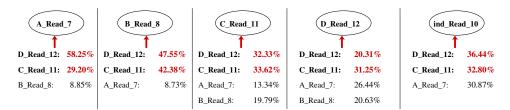

Fig. 10. Evictors for Each Reference

denotes the unique numerical identifier for this access instruction in the executable code of the target. This syntax is used in all the use cases presented in this paper.

The per-reference results show that different references have widely different behaviors. D\_Read\_12 and C\_Read\_11 have very high miss rates (> 87%) while the remaining references have lower miss rates (< 7%). The spatial reuse values are also much lower for D\_Read\_12 and C\_Read\_11, showing that on average, only 6.3% of the memory line data that was brought into the cache by these two references was accessed before eviction. The stream metrics show that accesses by D\_Read\_12 and C\_Read\_11 were completely unpredictable, with a regularity ratio value of 0.0. The remaining references had completely predictable access streams (regularity ratio=1.0) and were seen to be linearly strided (a single stride of eight for reference points of type double, a single stride of four for reference points of type int). All the preceding indicators show that D\_Read\_12 and C\_Read\_11 generate irregular accesses with very low cache hit rates. The evictors for each reference are shown in Figure 10. The figure shows that in addition to poor locality, the D\_Read\_12 and C\_Read\_11 references are also the top evictors for all the remaining references. Thus the references to D and C bring in data into the cache that is not reused (as indicated by their low spatial reuse values) and evict a significant amount of pre-resident data from the cache (as indicated by the per-reference evictors).

A look at the source code shows the cause of this behavior. The D\_Read\_12 and C\_Read\_11 references are potentially sparse indirect reads on an array, indexed by the array ind[]. The remainder of the read references (A\_Read\_7, B\_Read\_8 and ind\_Read\_10) are all direct array accesses, with regular single strided access patterns.

10.1.2 Optimization. From the analysis, we know that D\_Read\_12 and C\_Read\_11 are the key references with a significant impact on cache performance. We also know that these references inherently have poor cache reuse, due to their irregular data access pattern. Instead of trying to reorder their access patterns, we can try to reduce their detrimental impact on the cache by asking the memory system not to allocate a normal cache line for these references.

This is achieved using the concept of *reuse hints*. Reuse hints are tagged to each memory reference instruction (ld/st) and provide hints to the memory subsystem on the potential reuse of the data fetched by this access instruction. The Itanium2 ISA implements such a hinting mechanism [Intel 2004]. Hints indicate whether the accessed data has no expected temporal locality at the level of the L1 cache (hint=.nt1), at the level of the L2 cache (hint=.nt2) or no temporal locality at any level (hint=.nta). Floating-point accesses bypass the L1 cache. So, for these accesses, .nt1 refers to the *L2* cache and there is no .nt2 hint. For floating-point references with .nt1 or .nta hints that miss in the L2

|         |      |             |           |        |        | Miss  | Temporal | Spatial |

|---------|------|-------------|-----------|--------|--------|-------|----------|---------|

| File    | Line | Reference   | SourceRef | Hits   | Misses | Ratio | Ratio    | Reuse   |

| reuse.c | 7    | A_Read_7    | A[i]      | 101759 | 641    | 0.006 | 0.905    | 1.0     |

| reuse.c | 7    | B_Read_8    | B[i]      | 101760 | 640    | 0.006 | 0.905    | 1.0     |

| reuse.c | 13   | ind_Read_10 | ind[i]    | 14953  | 47     | 0.003 | 0.902    | 1.0     |

| reuse.c | 7    | A_Write_9   | A[i]      | 102400 | 0      | 0.0   | 1.0      | 1.0     |

Fig. 11. Optimized Per-Reference Memory Usage Statistics

cache, the L2 cache will allocate a cache line in only one out of the eight associative ways. The data in the remaining part of the cache is undisturbed. In addition, the LRU bits in the cache are not updated, so the allocated line will soon be selected for eviction.

We test our optimization on an actual Itanium2 system. We target the L2 cache, and tag the D\_Read\_12 and C\_Read\_11 references with ".nt1" hints. The hints will minimize the impact of these two references on the data pre-resident in the cache. In this way, we hope to retrieve any potential "locality" on the other references that was lost due to these two interfering references. We note that tagging C\_Read\_11 but not C\_Write\_13 will not provide the desired benefit since the line would be cached following the second access. This need to tag what appears to be a well-performing access demonstrates the complexity of the analysis that would be required by a compiler. The optimized code in the do\_mult() function is shown below:

```

10 void do_mult(void)

11 {

12    for(j=0;j < 1500;j++)

13    {

index=ind[j];

value = read_double_nt1(&C[index])

* read_double_nt1(&D[index]);

write_double_nt1(&C[index],value);

}

14 }

15</pre>

```

The read\_double\_nt1 and write\_double\_nt1 are special inlined functions that load and store doubles using instructions with explicit ".nt1" hints.

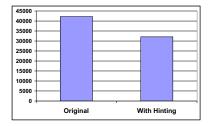

First, let us the see the potential impact of the optimization using the simulator. Our simulator currently does not support hinting for the access points. Instead, we run the same program again but without the  $D[\ ]$  and  $C[\ ]$  array accesses and see the change in cache metrics for the remaining references, as shown in Figure 11.

Notice the improvement in the hit rates for the A\_Read\_7, B\_Read\_8 and ind\_Read\_10 references as compared to the original behavior. The miss ratios for these references have decreased by an order of magnitude (e.g., 6% to 0.6% for A\_Read\_7 reference). The temporal fraction of the hits has gone up to 90% for these references, compared to the less than 3% in the original results. This indicates that we are now realizing intertimestep locality — the data is brought into the cache during the first time step and almost always remains in cache till it is accessed again during the next time step.

Let us now test our optimization on the real system. The original program and the opti-

Fig. 12. Comparison of L2 Cache Misses

mized version with cache hints were both compiled and run on an Itanium2 system. In each case, we monitor the hardware counters and count the number of L2 misses. Specifically, we measure the value of the L2\_MISSES event for the original and optimized program. The values for the two runs are shown in Figure 12. The number of L2 misses reduces from 42214 in the original program to 32072 in the optimized program (a 24% reduction).

We demonstrated how METRIC can be used for setting reuse hints. It is very hard or impossible for a static compiler to perform this analysis, since the complete run-time memory access pattern of the program must be considered (e.g., if the D\_Read and C\_Read hit in cache in the original program, the reuse hinting may actually be detrimental). The compilers evaluated (Intel icc 8.0, gcc 3.4) did not automatically set the non-temporal hints for the D\_Read and C\_Read. (For the optimized code, we inserted the hints manually using inline assembly functions).

#### 10.2 Use case: Prefetching

Consider the following snippet of C code:

```

0 #define MATDIM 1000

1

double A[MATDIM][MATDIM], B[MATDIM][MATDIM];

2

3

void do_mult(void)

4

{

5

for(i=0;i < MATDIM;i++)</pre>

6

for(j=0;j < MATDIM;j++)

7

{

8

A[i][j] = A[i][j] * B[j][i];

9

10

```

There are two two-dimensional arrays A and B. The function calculates the product of A[i][j] with B[j][i], and stores the value back into A[i][j]. This program was compiled on a Power4

machine using xlc<sup>2</sup>. A cache with the following parameters was simulated: cache size=32 KB, associativity=2, line size=128, writeback cache, LRU replacement policy. This configuration is similar to the L1 cache of a Power4 processor. The simulator reported

<sup>&</sup>lt;sup>2</sup>-O3 optimization level with loop unrolling turned off. Unrolling the loop body gives rise to many additional access instructions that show up as separate access points in the MHSim results. For clarity of presentation, we turn off unrolling the loop body so that fewer access points are present in the binary code. However, we could not prevent the compiler from unrolling the very last iteration of the inner loop, as explained in the text.

|        |      |           |                |        |        | Miss  | Temporal | Spatial |

|--------|------|-----------|----------------|--------|--------|-------|----------|---------|

| File   | Line | Reference | Source Ref     | Hits   | Misses | Ratio | Ratio    | Reuse   |

| test.c | 31   | B_Read_3  | B[j][i]        | 0      | 999000 | 1.000 | 0.0      | 0.0625  |

| test.c | 31   | A_Read_2  | <b>A[i][j]</b> | 936500 | 62500  | 0.062 | 0.0      | 1.0     |

| test.c | 31   | A_Write_7 | A[i][j]        | 999000 | 0      | 0.0   | 1.0      | 1.0     |

(a) Per-Reference Cache Statistics

|           | Total    | Predictable | Regularity | Average | # Distinct | % Stride         |

|-----------|----------|-------------|------------|---------|------------|------------------|

| Reference | Accesses | Accesses    | Ratio      | Length  | Strides    | Distribution     |

| B_Read_3  | 999000   | 999000      | 1.0        | 999     | 1          | stride=8000,100% |

| A_Read_2  | 999000   | 999000      | 1.0        | 999     | 1          | stride=8,100%    |

| A_Write_7 | 999000   | 999000      | 1.0        | 999     | 1          | stride=8,100%    |

(b) Per-Reference Stream Statistics

Fig. 13. Original Per-Reference Memory Usage Statistics

|                                  | miss ratio     | = | 0.3541  | spatial reuse | = | 0.17836 |

|----------------------------------|----------------|---|---------|---------------|---|---------|

| the following cache performance. | temporal ratio | = | 0.51613 | spatial ratio | = | 0.48387 |

| the following cache performance: | misses         |   |         | spatial hits  |   |         |

|                                  | hits           | = | 1937499 | temporal hits | = | 1000000 |

Notice the high miss ratio (35%) and the relatively low spatial reuse value (17.8%). The per-reference results are shown in Figure 13. Figure 13(a) shows the metrics generated by the cache simulator, and Figure 13(b) shows the stream metrics generated by the PRSD detector. Due to instruction scheduling, the compiler unrolls the very last iteration of the innermost loop, hence there are several additional access instructions present in the executable (more than the three access instructions in the original C code). For clarity of presentation, we do not show the metrics associated with these additional access points. This explains why the number of accesses for the references shown in the per-reference result do not exactly match the number of accesses expected from the C source version.

10.2.1 Analysis. B\_Read\_3 has the worst possible cache performance — all of its accesses are misses. This also causes the very low spatial reuse value, showing that less than 7% of the data cached by the B\_Read\_3 reference is actually accessed by the processor before the memory line is evicted from cache. The stream metrics show that B\_Read\_3 generated extremely predictable accesses (regularity ratio=1.0) with long stream lengths (average length=999) and only a single stride. The stride value is very large (8000), so no spatial locality is realized (since successive accesses map to different cache lines).

In contrast, A\_Read\_2 has very good cache performance with excellent spatial reuse (100%). The stream metrics show that accesses generated by A\_Read\_2 were also completely predictable (regularity ratio=1.0) with a long average stream length. In contrast to B\_Read\_3 though, A\_Read\_2 generated *single strided* accesses (of stride eight, the size of the double data type)). This ensured that A\_Read\_2 achieved excellent spatial locality

(spatial reuse=100%).

Upon closer inspection of the source code, we observe that the innermost loop (j loop) has a stride-1 traversal over the innermost dimension of the array A, which result in the accesses generated by the A\_Read\_2 reference. In contrast, the accesses to array B are generated with the innermost j loop iterating over the *outermost* dimension of array B, leading to the high stride value (8000) seen for B\_Read\_3.

10.2.2 Optimization. The key idea is that both A\_Read\_2 and B\_Read\_3 generate completely predictable accesses. We exploit this fact to *prefetch* the array elements long before they are used to reduce the effective access latency. The average stream length for both access points is high, indicating that prefetching would be profitable, and the number of distinct strides is low, reducing the number of potential prefetch target addresses.

We evaluate this optimization on a Power4-based platform. This platform already has a hardware stream prefetcher that detects cache misses mapping to consecutive memory lines, such as frequently generated by stride-1 accesses. Once such a pattern is recognized, the prefetcher automatically prefetches the consecutive memory lines into cache [Tendler et al. 2002]. Hence on this platform, there is no need to insert explicit prefetch instructions for the A\_Read\_2 access point as it generates only stride-1 accesses. In contrast, accesses generated by B\_Read\_3 will not be prefetched by the hardware prefetcher, since they do not map to consecutive memory lines (stride 8000). Hence, we target these accesses for prefetching.

We use the "Data cache block touch" (dcbt) prefetch instruction. The optimized code is as follows:

```

0 #define MATDIM 1000

1

double A[MATDIM][MATDIM], B[MATDIM][MATDIM];

2

3

void do_mult(void)

4

{

for(i=0;i < MATDIM;i++)</pre>

5

6